一種基于DDS和Qt的“所見即所得”波形發生器

0 引言

隨著電路設計的多樣化,電路測試也對信號源提出了更高的要求。傳統的信號源只能產生幾種固定的波形,靈活度較差。任意信號發生器(AWG)很好地滿足了這個要求,它不僅可以輸出標準信號,而且可以方便地產生任意波形,在測控、通信,醫療等領域有著廣泛的應用。任意信號發生器通常采用直接數字頻率合成(direct digital frequency synthesizer,DDS)技術實現。DDS技術是J.Tiemev在1971年首次提出的一種以全數字技術,它從相位概念出發直接合成所需波形的一種新的合成原理。Qt是一個跨平臺的C++圖形用戶界面應用程序框架。它提供給應用程序開發者建立圖形用戶界面所需的所用功能。Qt是完全面向對象的,模塊化程度非常高,很容易擴展,并且允許真正地組件編程。 Qt具有優良的跨平臺特性,支持多種系統和平臺,包括Windows系統,所有的UNIX系統以及嵌入式系統等。Qt遵循GPL(general public lice-nse)協議,開放主要的源代碼,用戶可以在GPL的規定下自由添加新特性。

1 DDS模塊的設計

1.1 DDS在FPGA中的實現

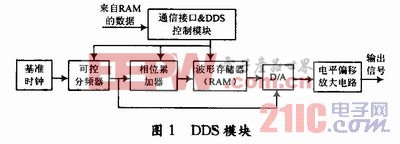

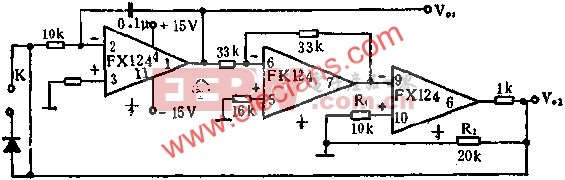

DDS由相位累加器,波形存儲器,D/A轉換器,低通濾波器等部分組成。該系統的DDS模塊根據需要做了適當的修改。其結構框圖如圖1所示。

(1)增加了通信接口電路和DD8控制模塊用于接收用戶數據和控制DDS的運行狀態。

(2)基準時鐘采用5 MHz,經過可控分頻器分頻后作為DDS的時鐘信號,周期分辨率最高可達200 ns(即分頻為1)。

(3)相位累加器的頻率控制字固定為1,相位控制字固定為0。

(4)波形存儲器采用RAM,可以寫入用戶自定義的波形數據以產生任意波形,其地址寬度設置為11 b,這樣存儲深度可達2K點。

(5)電平偏移電路用于消除D/A輸出信號中疊加的無效直流分量,對于有效的直流分量會保留。

1.2 通信接口及控制寄存器的設計

DDS控制寄存器控制整個DDS模塊的運行參數和狀態,并通過通信接口接收來自ARM的數據。根據需要共設置了8個寄存器,地址從O~7。其功能和分配如表1所示。

表1其中:

(1)0~3 B存儲分頻參數,占用32位,因此分頻范圍為1~232。

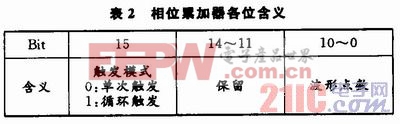

(2)4~5 B存儲相位累加器的參數,用于控制波形點數和觸發模式,其各位的含義如表2所示。

評論