基于NiosII的便攜式超聲波流量計設計

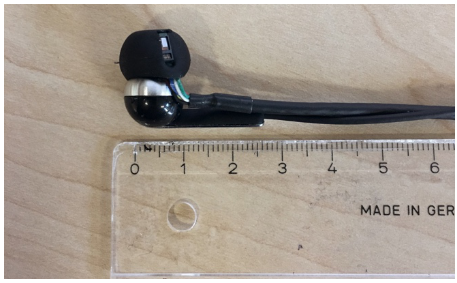

系統超聲波換能器驅動信號是由微處理器產生的,微處理器產生一個200 kHz的矩形脈沖信號,經光耦隔離后進入功率放大電路。根據換能器的特點,該矩形脈沖信號占空比為2%。超聲波換能器激勵信號如圖3所示。本文引用地址:http://www.104case.com/article/187622.htm

2.2 超聲波信號處理電路

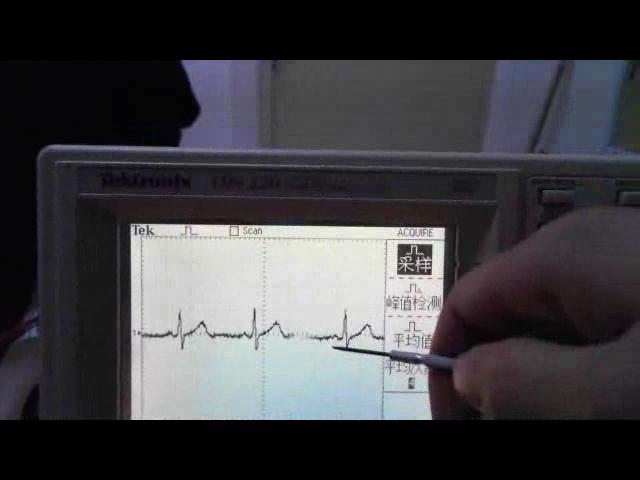

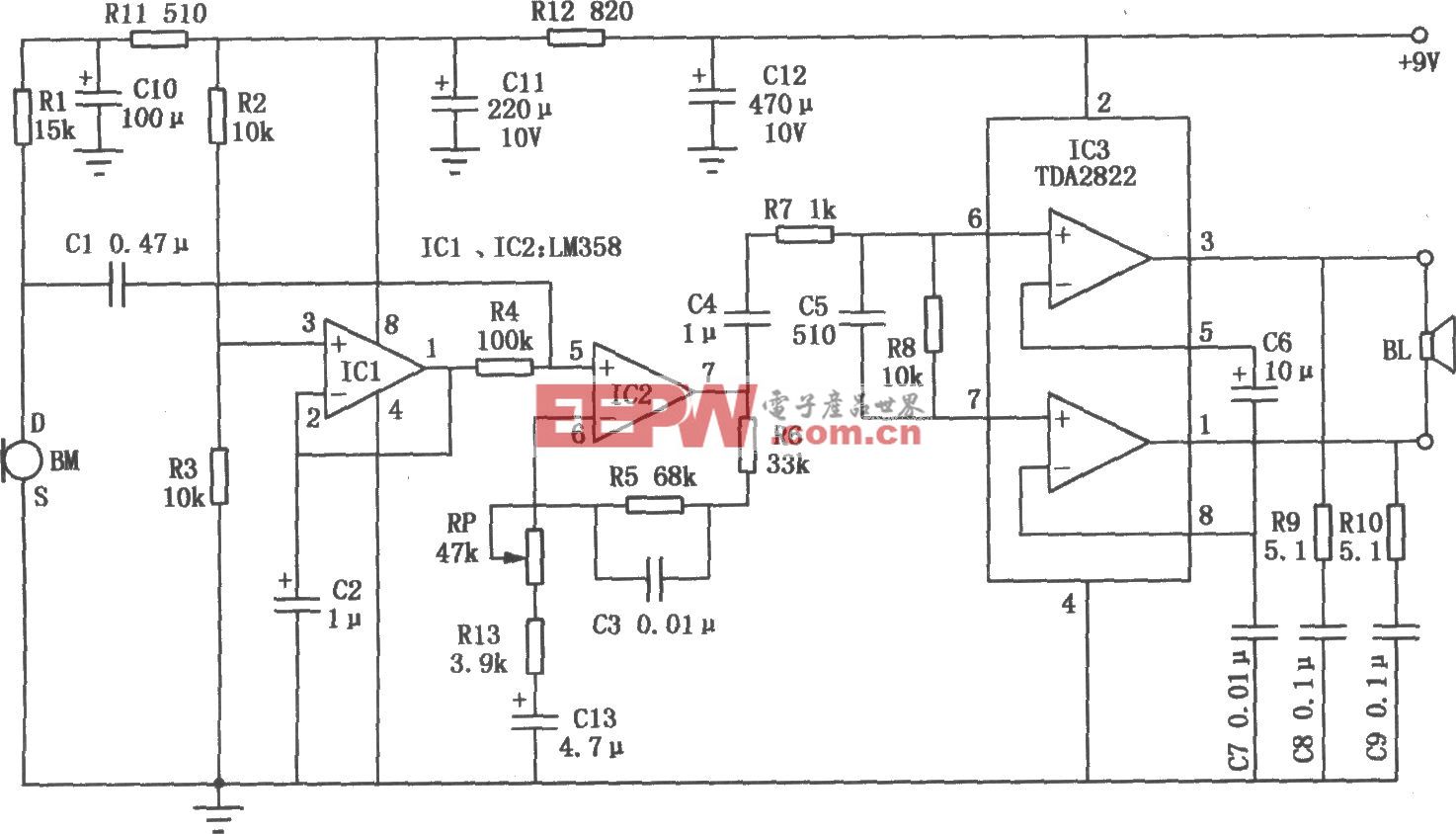

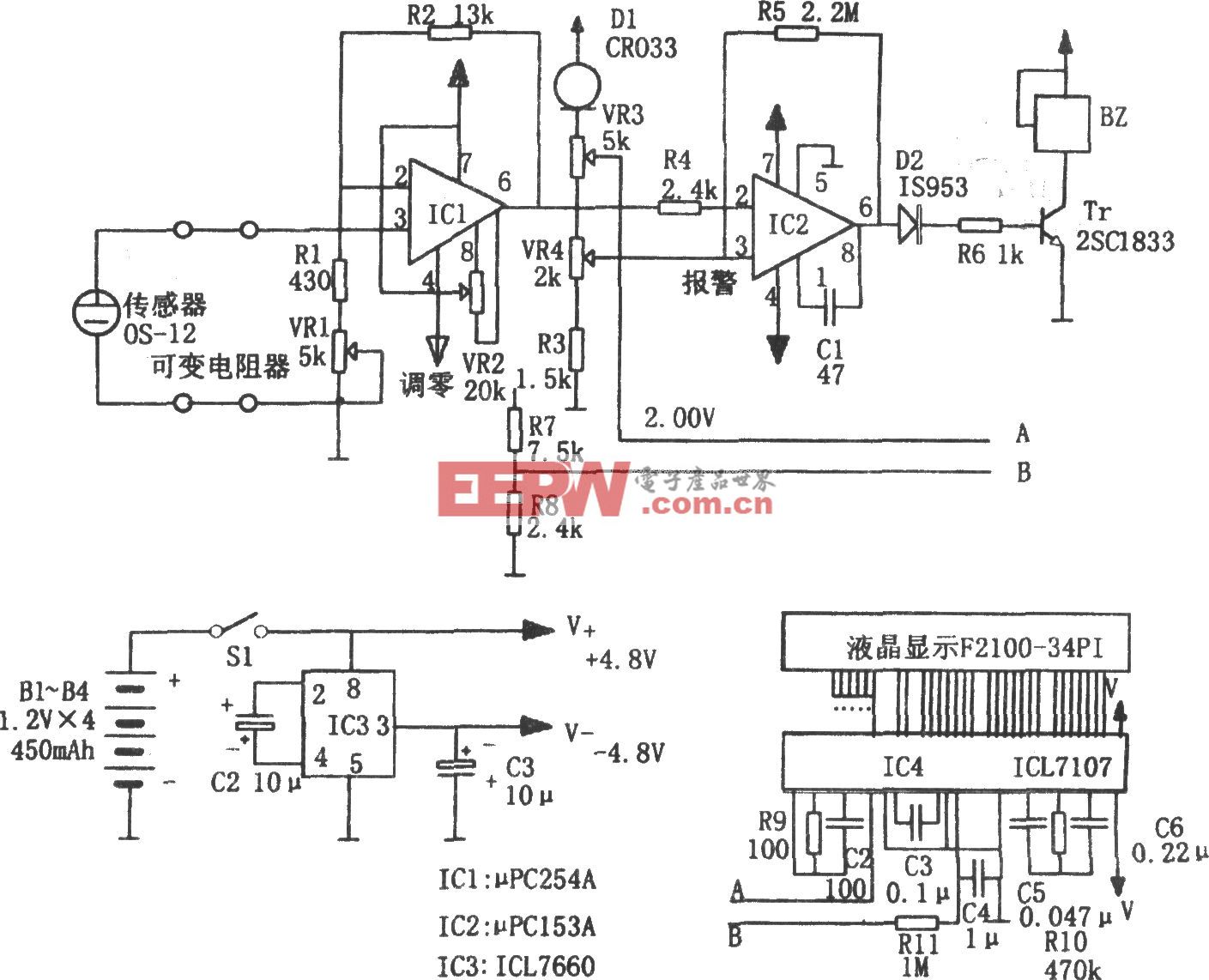

超聲發射換能器發射的超聲波信號,經過管壁和流體,衰減比較大,因此超聲波接收換能器接收的信號比較微弱,通常只為幾十mV數量級,這時放大器的噪聲對測量精度的影響也比較大。同時,由于超聲波流量計中使用的超聲波頻率較高,所以要求運算放大的增益帶寬積足夠高,因此該級電路采用低噪聲高速運算放大器。本系統中選用MAX410作為放大器。

在超聲波流量計工作的過程中,由于振動、流動及工業現場的管道噪聲和變頻設備的電噪聲等電子干擾,會引起周期性的噪聲信號出現,并導致在相關圖上出現周期性波峰。當其疊加到流動噪聲的相關曲線上,會使真實的渡越時間對應的波峰不明顯,甚至被其他的波峰掩蓋,無法得到正確的測量結果。通過低噪聲高速運算放大器對信號進行放大后還需要對信號進行濾波。本系統中的濾波電路為帶通濾波。系統中換能器發射接收的超聲波中心頻率為200 kHz,所以需要設計一個中心頻率為200 kHz的帶通濾波器,它可以使200 kHz的超聲波信號順利地通過,而阻止或衰減非200 kHz的超聲波信號及其他干擾信號。

另外,超聲波信號在管道中傳輸時,由于各個聲道長度不同,傳感器特性存在差異,氣體介質不同以及測量時氣體流速的變化,導致每次測量時傳感器接收信號的幅度也不同。為了后端進行高精度的計時,需要自動增益控制對接收信號的大小進行調節,使接收信號有一個穩定的幅度,從而滿足系統測量高精度的要求。

3 數字電路設計部分

3.1 概述

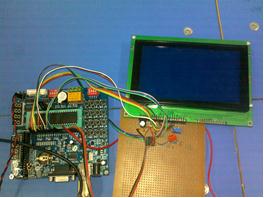

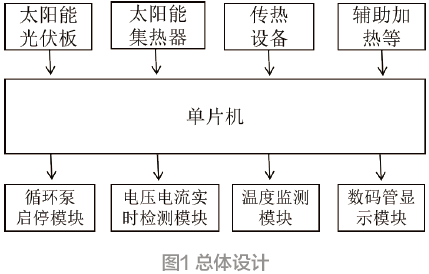

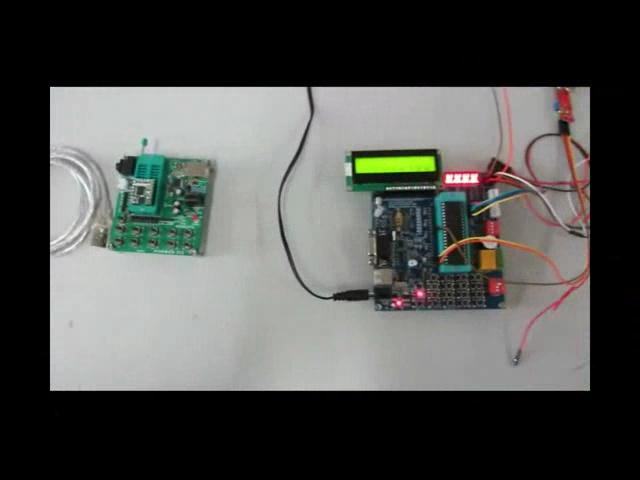

本系統數字電路設計部分的核心是FPGA。在本系統中FPGA主要實現兩部分功能:一是實現高精度計時,為準確測量流速提供保證;二是通過構建軟核CPUNioslI來實現對整個系統的控制。本系統選用Altera公司Cyclone II系列的EP2C8Q208C8N芯片。

關于計時這里不再贅述,主要就是通過MEGA WIZARD調用PLL模塊實現倍頻到200 MHz然后供給計數器模塊來計數,計數結果通過移位寄存器來上傳給CPU,再通過CPU處理后傳給上位機。

NiosII是32位RISC嵌入式處理器,它是Altera公司的第二代FPGA嵌入式處理器,其性能超過200DMIPS,在Altera FPGA中實現僅需35美分。特別是,NioslI系列支持使用專用指令。專用指令是用戶增加的硬件模塊,它增加了算術邏輯單元(ALU)。用戶能為系統中使用的每個NiosII處理器創建多達256個專用指令,這使得設計者能夠細致地調整系統硬件以滿足性能目標。NiosII系列支持60多個外設選項,開發者能夠選擇合適的外設,獲得最合適的處理器、外設和接口組合,而不必支付根本不使用的硅片功能。基于其嵌入式的特點以及其成本,NiosII特別適用于便攜式儀表方面的應用。

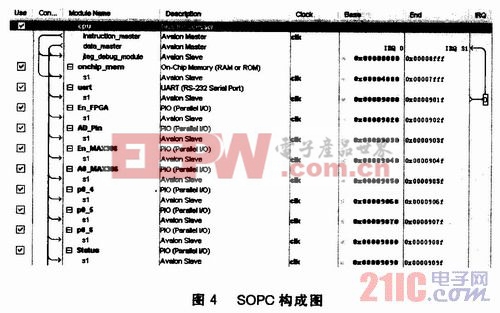

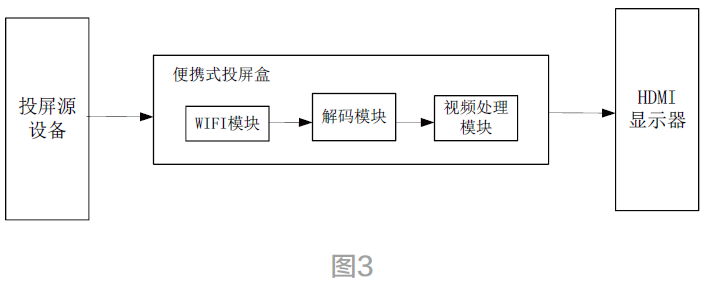

3.2 SOPC的硬件構建

通過Quartus中的SOPC Builder來構建SOPC系統。首先要添加一個CPU。為了節省片上資源,選用經濟型的CPU,外部晶振是50 MHz。程序運行內存直接選用0n-Chip Memory,因為EP2C8Q208C8N片上的RAM空間大概有20 KB左右,通過優化,片上內存完全能夠滿足程序的需要,這樣就不必添加外接的SDRAM芯片,減少了PCB板的面積,大大降低了成本。代碼優化方法是通過NioslI IDE里面的System Library Proper-ties來設置:依次選中Program Never Exit,Small C Library,Reduced Device Drivers,Lightweight Device Drivers API,取消選中

Support C++并設定Optimize Size為-0s級,這樣就可以有效的縮減程序代碼。

另外,為了向上位機傳遞測試數據,需要添加UART。這里添加的UART只是一個協議,與上位機實現通信,還需要在外圍添加電平轉換芯片MAX232以實現與上位機的正常通信。

為保證系統正常運行,添加內部定時器實現看門狗功能,另外需要添加的就是一些PIO接口。能夠產生中斷的PIO口注意要分給一定的中斷號。CPU的Reset Vectot。地址和Exception Vector地址都設為On-Chip Memory,并讓系統自動分配基地址以及中斷。點擊Generate生成整個SOPC,圖4即為整個SOPC的構成圖。

3.3 用Niosll IDE編寫整個系統的控制程序

NiosII IDE(Integrated Development Environment,集成開發環境)提供了完整的C/C++軟件開發套件,包括編輯器、項目管理器和構建工具、調試器和兼容CFI(Common Flash Interface)的Flash編程器。調試器連接多種目標系統,包括FPGA硬件(通過JTAG電纜)、NioslI指令集仿真器和Modelsim-Altera軟件,因而能夠提供最靈活的調試方案。

為了方便用戶編程,NiosII為用戶提供了設備驅動程序,也就是硬件驅動層數據庫HAL。軟件編寫人員只要利用HAL提供的各種函數就能編寫應用程序,從而方便地與底層硬件進行通信,而無需關心底層硬件的實現細節。HAL系統庫可在IDE創建一個新工程時,由系統自動生成。

評論