一種基于PCI總線的反射內存卡設計

FIFO 控制器內部各模塊功能如下:

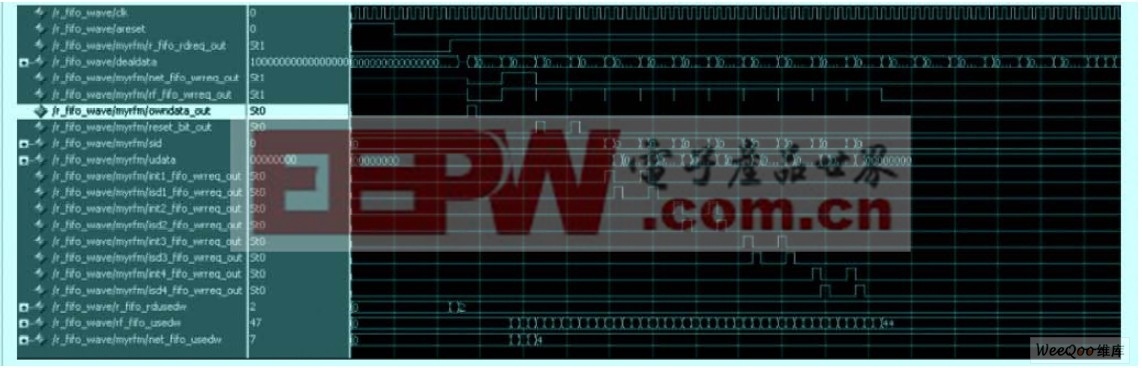

(1) 數據解析對從網絡中接收的數據進行判斷,如果是中斷事件將中斷數據寫到中斷FIFO 中,如果是需要共享的數據則一部分送到SDRAM 控制器,一部分送仲裁機構;(2) 數據封裝對本節點發送的數據重新打包,加入數據類型、數據包長度、發送節點ID、目標節點ID 及校驗等相關信息,以便于其他節點對數據進行解析;(3) 仲裁機構對來自接收FIFO 的數據和本節點發送到數據進行仲裁, 當他們同時到達時來自接收FIFO的數據優先;(4) 讀信號產生器在接收到半滿中斷時產生讀信號,從接收FIFO 中讀出相應的數據,避免FIFO 充滿或溢出;(5) 寫信號產生器在仲裁機構向下發送數據時給發送FIFO一個寫信號。FIFO控制器仿真時序如圖4所示。

圖4 FIFIO 控制器仿真時序

2.3 編解碼控制器

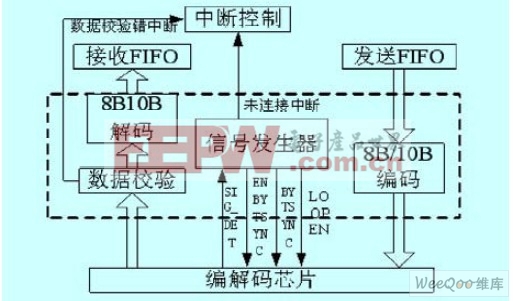

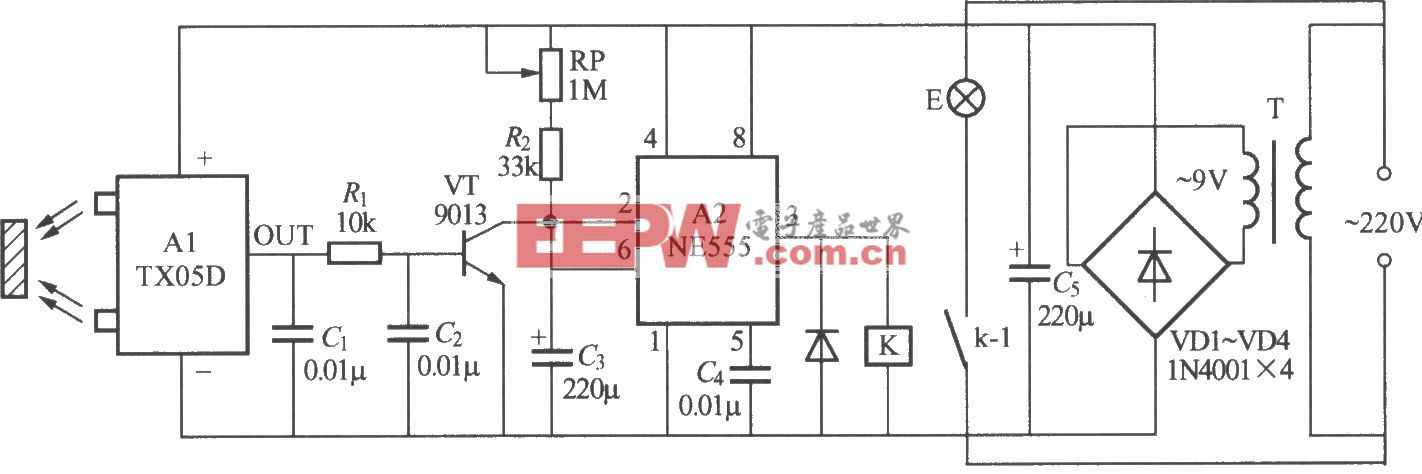

編解碼控制器由信號產生器、數據校驗、8B/10B編碼、8B/10B 解碼組成。編解碼控制器結構如圖5 所示。在這部分主要是進行數據8B/10B 編解碼,以與編解碼芯片數據格式匹配同時給編解碼芯片的正常工作提供控制信號,數據編解碼控制器仿真時序如圖6 所示。

圖5 編解碼控制器結構圖

圖6 數據編解碼仿真時序

評論