提升ADC分辨率的電路設計

在模擬多路復用器達到穩定之后,快速比較器IC1立刻完成適當的增益設置。比較器的閾值電壓使信號被IC6 和IC7放大后不會飽和或嵌位。AD8561 比較器的響應時間為7 ns,它提供一個鎖定信號,能夠在放大器達到穩定期間和ADC捕獲信號期間保持增益不變。通常的PGA配置要求用戶在輸入端施加信號之前預先設置放大器的增益。圖2中的PGA具有自動設置增益范圍的特點,它能夠選擇最適當的PGA增益以獲得最高精度而不引起信號飽和或嵌位。比較器包含滯后電路,以便在信號接近某一個具體增益范圍限制時減少設置的增益變化。該電路能自動將ADC的精度提高到19位,同時又能保持其1MSPS的全速采樣速率。

IC6 使用1或8的增益設置對多路復用器的輸出信號進行放大,如果需要提供最大可達到25的不同增益,可以改變反饋網絡電阻。模擬開關IC3控制增益的設置。運算放大器AD8021的高增益帶寬乘積能提供足夠的帶寬,因而其補償電容對所有的增益保持相同。放大器IC7 為ADC產生差分輸入信號。比較器和放大器的建立時間以及ADC的捕獲時間都遠小于ADC 的1μs的轉換時間。ADC兩個輸入端的RC噪聲濾波器R1/C1和R2/C2,它們占用額外時間。這些濾波器限制PGA的噪聲帶寬。當IC7 的增益為-1時,PGA是數據采集系統主要的噪聲源。

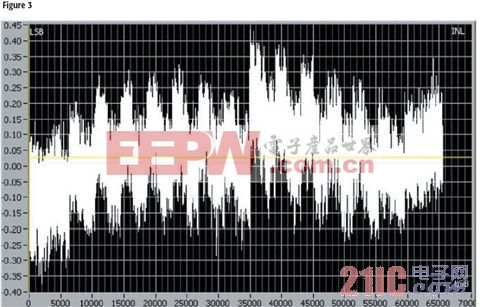

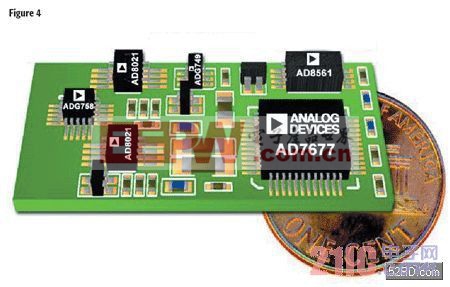

圖3示出該電路設計的線性誤差。在這種最高增益設置條件下達到如此低的線性誤差(圖中示出最大值為0.44 LSB,最小值為-0.37 LSB)并非易事。這相當于±0.9 ppm的典型誤差。當增益為8時,輸出噪聲為85 μV rms。如果需要,可以利用軟件平均進一步減少噪聲。圖4示出使用AD7677評估板構成的完整數據采集系統,印制電路板面積為15×30 mm。

See Fig 3 of original article)

圖3 數據采集系統對于所有可能ADC數字量的線性誤差

圖4 以1美分硬幣為參照的完整數據采集系統的相對尺寸

評論