基于TMS320C6455的視頻動目標檢測裝置設計

1.4 數字圖像序列導入

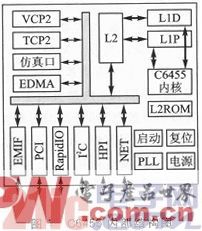

數字圖像的處理主要在DSP中進行,為了提高圖像處理的速度,需要借助其強大的EDMA功能。TMS3206455提供由增強型直接存儲器訪問EDMA(Enhanced Direct Memory Address)控制器,無需CPU的參與就能夠完成存儲器映射空間的數據傳輸,可以滿足多種海量數據交換的處理系統需求。

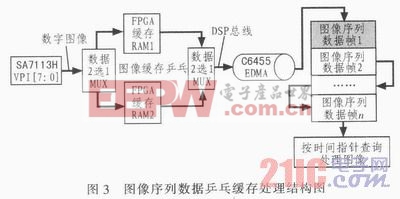

數字圖像序列的導入和DSP內部存儲均采用了RAM乒乓結構進行。在FPGA中主要完成YUV422數字圖像的乒乓緩存,在DSP中主要完成數字圖像序列的乒乓處理和循環存儲,結構組成如圖3所示。本文引用地址:http://www.104case.com/article/187433.htm

FPGA的圖像乒乓緩存以行(512像素)為單位,依據FPGA內部的RAM資源來確定乒乓緩存空間的大小,利用行同步時鐘(或其分頻信號)來同步實時寫入圖像數據。由于DSP的EDMA速度資源空間很大,即使內部資源很小的FPGA,只要其內部RAM空間超過1 k(512x2像素,2行圖像數據),就能夠實現該乒乓結構。

DSP則利用時間指針進行圖像序列的乒乓循環存儲和處理,在EDMA實時導入當前場的圖像的同時,完成對上場圖像的算法處理。這樣的乒乓結構可以根據DSP的內存空間的大小和算法的需求進行合理的設計,乒乓循環幀數n=2,3,4…。

TMS3206455內部提供有2 096 K字節的L2 SRAM空間,除了預留程序、數據存儲、算法空間外,還可以提供至少8場(8x512x256=1 024 KB)圖像的存儲空間,系統還可以備選DDR2作為擴展內存,為圖像序列的乒乓緩存提供了充足的高速存儲空間支持。

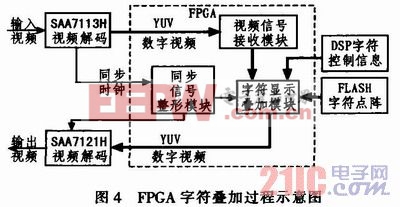

1.5 字符疊加

為了讓觀測者更清楚地了解目標的信息,視頻處理裝置通在顯示圖像上實時疊加字符,采用的方法是在圖像上直接進行模擬或數字信號疊加。本裝置的字符疊加采用Philips公司的視頻編碼芯片SAA7121H完成,顯示信息可以通過DSP進行動態控制,保證信息的實時、直觀。

TMS3206455通過I2C總線對SAA7121H進行配置,在FPGA中對SAA7113H輸出的YUV視頻信號進行處理并提取同步信息,作為后面字符疊加的同步控制信號。需要疊加的字符點陣庫存儲在FLASH中,由DSP控制的實時顯示字符內容存儲在FPGA的RAM中;在視頻同步信息的控制下,字符疊加模塊在視頻信號的特定(顯示)位置讀取RAM中的數據,并將字符點陣與視頻信號進行疊加,產生所需的帶字符的視頻。視頻字符疊加過程如圖4所示。

評論