TLM驅動式新方案探討

引言

本文引用地址:http://www.104case.com/article/187359.htm Cadence設計系統公司提供一種全面的SystemC TLM驅動式IP設計與驗證解決方案,包括方法學指南、高階綜合、有TLM感知的驗證以及客戶服務,推動用戶向TLM驅動設計與驗證流程轉變。

下一個抽象級別建立在事務級建模(TLM)基礎之上。創建TLM IP作為黃金源碼后,設計團隊可簡化IP創建和復用,在功能驗證上節省人力物力,并減少bug。設計迭代減少,原因是TLM驗證比RTL驗證快得多,且架構選擇在RTL驗證進行之前就能得到確定。此外,事務級模型可用于軟硬件協同驗證,并可組成用于早期軟件開發的虛擬平臺的一部分。所有這些優勢將大幅提升設計效率。

TLM通過函數調用而非信號或線路進行模塊間通信。它允許用戶分析讀或寫這些事務,而不用擔心底層邏輯的實現和時序。SystemC是開發可復用、可互用TLM IP的最佳語言標準。此外,因為SystemC建立在C++基礎上,它還允許對C語言算術函數的完全復用。開放SystemC行動(OSCI)為TLM模型定義了若干抽象層,分別是程序員視角(無定時)模型、寬松定時模型和近似定時模型。

要求對RTL進行改變的關鍵難題

在RTL中,有限狀態機的結構要進行充分描述。這意味著,在編寫RTL時需關注微架構詳情,如存儲器結構、流水線、控制狀態或最終實現中使用的ALU等。 這一要求導致更長、可復用性更低的設計與驗證流程。

有時當TLM用于當前流程時,現有的基于RTL的流程需要進行兩次設計意圖手工輸入——一次在系統級、一次在RTL級。這種過程粗笨低效且易出錯。架構直至產生RTL后才能確定,而重新確定IP目標成本很高。一個真正的TLM驅動式設計與驗證流程將只需要一次設計意圖簡單的表達,并提供一條自動化的轉換方法。

從RTL開始查找和解決架構問題過程長,代價高

RTL驅動式設計方法學的一大問題是,一種架構是否能實現,直到建立了RTL并對其進行驗證后才能確認。由于RTL是架構的直接表示,大部分RTL設計師不得不同時探究功能正確性、架構和設計目標。這導致很長的周期,始于做出架構決定,終止于驗證功能性。通常,設計與驗證團隊會發現需要修改架構的功能性bug,每次發現這樣的bug就需要重新開始整個周期。

在RTL上復用IP設計限制了架構靈活性

當今SoC中,可能有高達90%的IP模塊來自以前項目的復用。但是,當IP的黃金源碼為微架構級別時,復用是很困難的。重定RTL IP的微架構目標費力且容易出錯。目標系統應用可能差別很大,意味著不通過重新架構,僅通過簡單復用,新的SoC設計目標是不能達到的。例如,RTL設計師可能需要將設計重新分割成RTL塊、改變流水線級數、或創建新的存儲器架構,因為在原有IP中,這些微架構詳情都是固定和預先決定的。

RTL功能驗證時間比當前技術的最高吞吐量增加得更快

在很多SoC項目中,功能驗證已成為主要瓶頸。RTL功能驗證開始時,在系統級的大量驗證投入已然損失。雖然驗證規劃、指標驅動式驗證等方法使設計團隊尚能應付當前的大部分驗證難題,但時間限制和日益增多的門數正在使驗證變得難以為繼。RTL功能驗證所需時間可能隨設計的增大而呈指數式增長,因為相互作用的各種模式及該IP需要測試的許多軟硬件配置導致了各種極端情形,它們也需要進行驗證。

RTL是有精確時鐘周期的,涉及的代碼行遠多于TLM邏輯。對RTL模型進行仿真時,仿真器檢查所有事件或時鐘周期,即使在協議級上并未發生任何重大情況。仿真器要在微架構詳情上浪費大量機器周期,而這些需要在架構確定后才能確認。TLM仿真在更高抽象級別進行,能更早完成,并提供更高性能。

TLM正是需要的解決方案

TLM驅動的設計和驗證流程可實現在功能級別上描述IP,然后在快速仿真中驗證事務的功能行為。TLM流程的主要優點包括能更快創建設計;減少了黃金源碼中的代碼行;bug更少;表達設計意圖更容易,且僅需一次;更快的仿真和調試;功耗預估可更早進行;支持軟硬件協同驗證;可將模型納入虛擬平臺;RTL生成前可進行架構驗證;在RTL驗證中可復用TLM驗證IP;無需微架構重新設計即可進行IP復用;ECO模式下產生的RTL變化很小。

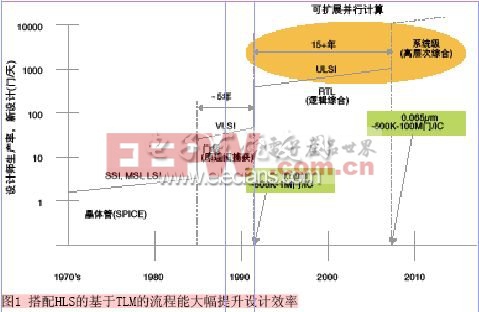

基于TLM的流程與高層次綜合(HLS)配合,可將抽象級別提高。這是大約15年前設計師轉向RTL后的又一次重大轉變,根據之前的經驗,這次轉變有可能使設計效率呈現數量級的提升(見圖1)。

下面幾部分描述了TLM驅動式設計和驗證流程的具體屬性和優勢。

創建TLM作為黃金源碼

——更快的IP創建與設計IP復用

與RTL不同的是,TLM不描述最終實現的微架構詳情。不描述微架構詳情大幅提高了TLM設計在要求各不相同的多個項目間的可復用性,因為相同的TLM IP可重新定為不同微架構的RTL代碼。而且,得益于更高的抽象程度,正確地創建功能要容易得多。TLM模型具有的代碼行比對應的RTL模型要少得多,從而在最終設計中實現了編碼效率和品質的同步提高。

開發與維護作為IP模塊黃金源碼的TLM所需的綜合和驗證解決方案,需要產生有品質保證的結果并驗證其正確性,且無須編輯RTL或門級設計。這使設計團隊在TLM環境內就能做出所有決定,并可通過將TLM源碼復用于系統來約束完全不同的其他設計。

SystemC是描述事務級設計的最佳標準,并連接到實現,提供了最好的可復用機會。它可對硬件的并發特性進行建模,并針對進程、管腳、線程和控制邏輯描述定時或非定時的行為。TLM 1.0和2.0標準提供了創建可互用IP模型的能力。最終,需要有一個合格的可綜合TLM IP庫,及可綜合TLM標準(或事實上的)子集。

電子血壓計相關文章:電子血壓計原理

評論