中頻數字化正交解調結構介紹

傳統的中頻數字化正交解調系統中芯片選擇的限制及成本的大幅上升。為此提出了一種新的中頻數字化正交解調系統結構,在保留高速A/D的高數據率輸出的同時,大幅降低現場可編程門陣列工作頻率,并進行了仿真,驗證了系統結構的可行性。

本文引用地址:http://www.104case.com/article/187263.htm1 數字正交解調原理

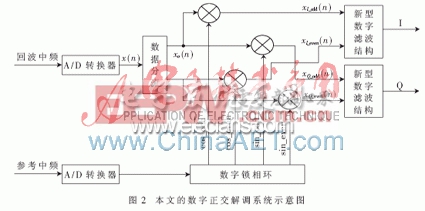

數字正交解調結構如圖1所示,參考和回波中頻模擬信號經由2個A/D轉換器同步采樣量化,然后把數據送入現場可編程門陣列(FPGA)中實現數字下變頻。在FPGA中,將參考中頻的采樣結果輸入數字鎖相環進行鎖相之后,產生2路正交的數字中頻載波信號。分別與回波中頻信號的采樣結果相乘,實現頻域的搬移。再分別進行數字濾波得到I、Q 2路正交數字基帶信號后,將數據輸出至后端數據處理單元。

2 數據正交解調系統設計

圖2所示為本文提出的中頻正交解調結構框圖,針對高速A/D轉換器數據率大的特點,在FPGA內部,通過DEMUX將回波中頻采樣數據x(n)拆分為奇序列xo(n)和偶序列xe(n),分別進行處理,使數據速率降為原先的一半。同時,為了使載波序列與X(n)拆分后序列正確匹配相乘,數字鎖相環輸出調整為2組4路載波信號: cos_odd與sin_odd、cos_even與sin_even與相應的回波拆分序列相乘。得到4路混頻信號xl_odd(n)與xl_even(n), xQ_odd(n)與xQ_even(n)輸入數字濾波器。

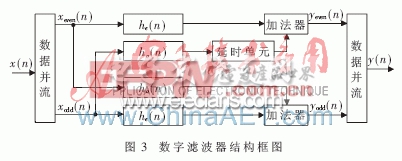

由式(3)、式(5)可得一種新的數字濾波器結構形式(見圖3),其特點在于將數字信號序列拆分為2路,同時將濾波器系數拆分成2個子濾波器,通過2個子濾波器對2路拆分信號的濾波輸出組合得到對原數字信號序列濾波輸出的奇數項和偶數項。經過上述處理,子濾波器的工作頻率可降為原濾波器頻率的一半,因此在具體實現時可獲得比原濾波器更高的工作頻率,這樣合成濾波器的工作頻率可達到原濾波器工作頻率的2倍以上。

最后將2組混頻輸出信號xl_odd(n)與xl_even(n),xQ_odd(n)與xQ_even(n)分別通過2個數字濾波器后,就可以得到解調后的正交基帶信號I,Q。

評論