基于Arrhenius模型快速評價功率VDMOS可靠性

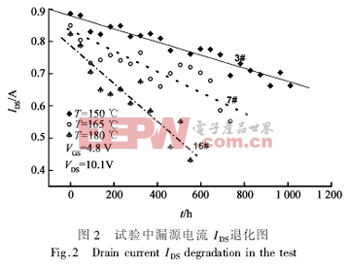

圖2為試驗中漏源電流IDS退化圖(3#、7#、15#為例),其偏置均為VDS=10.1V、VGS=4.8V。可以看出在三組溫度應力作用下,漏源電流IDS均出現不同程度的下降,且隨著應力的增大,下降幅度增加,溫度應力加速器件參數退化,與阿列尼斯方程符合較好。

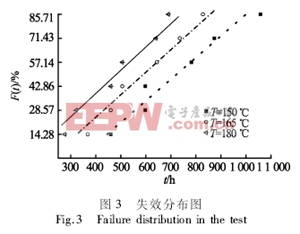

本試驗的失效分布圖如圖3所示,由圖看出本試驗在三組溫度應力下,樣管的失效分布呈三條相互平行的直線,說明在該試驗中樣管的失效機理是一致的,且由圖可知較高的溫度應力可以更快地加速參數退化,器件達到失效所需時間更短。此結果與恒定應力加速壽命試驗理論相符,說明本試驗是一個比較成功的恒定應力加速壽命試驗。

3.3 數據分析

本試驗樣本容量小,故采用精度較高的“最好線性無偏差估計”(BLUE)法進行數據處理。結果如下:①功率VDMOS在室溫下(結溫117℃)工作時的壽命特征值為3.67×106h;②功率VDMOS的主要失效模式是漏源電流的退化,其失效激活能E=0.54eV;③形狀參數m的加權平均值m=1.373;④加速系數τ:τ(240~117℃)≈47.9145,τ(255~117℃)≈67.8953,τ(270~117℃)≈94.3733。

4 結果分析

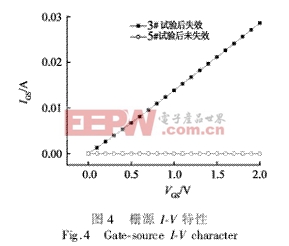

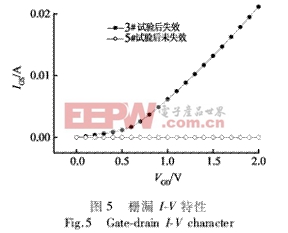

對三組試驗中的失效樣管進行結之間(pin-to-pin)電特性測試(第三端開路)。圖4、5所示分別為失效樣管(以3#為例)與未失效樣管(以5#為例)的柵源I-V特性及柵漏I-V特性比較。

從失效樣管的柵源I-V特性及柵漏I-V特性可以判斷其柵極出現較大漏電流,說明柵極失去其絕緣能力,發生柵極累積失效。

由VDMOS工作原理可得,柵極發生失效時,其失去絕緣能力,因此當p區反型形成溝道時,部分電子通過已擊穿的柵極形成柵極漏電流,使得形成漏源電流的電子減少,造成漏源電流IDS降低。通過上述試驗及理論分析可以確定漏源電流的下降是由柵極累積失效而引起的。進一步的柵極失效原因正在研究中,其結果將在后續工作中給予介紹。

5 結論

對功率VDMOS在高溫環境下進行恒定應力加速壽命試驗得到:

①室溫下工作時(結溫117℃),其壽命特征值t=3.67×106h,失效激活能E=0.54eV,這些較為完整的可靠性數據為功率VDMOS類型器件在今后的生產和應用中提供參考價值。

②恒定應力加速壽命試驗中功率VDMOS的主要失效模式是漏源電流IDS的退化,其失效機理是柵極累積失效。

評論