基于TMS320VC5509與AD7322的數據采集系統的設計

1.4 DSP模塊

DSP芯片采用Ti公司的TMS320VC5509,它是一種高性能、低功耗、定點數字信號處理器,其主要特點如下:

1)最高主頻能夠達到144MHz,指令周期6.94ns。

2)CPU的內部總線結構包括一條程序總線,三條數據讀總線,兩條數據寫總線及用于外設和DMA控制器的總線。這些總線使得C5509能在一個時鐘內完成三次數據讀操作和兩次數據寫操作。5509還擁有兩個乘法累加器(MAC),每個累加器都能夠在一個周期內執行一個17bitx17bit的乘法運算。

3)128 kx16 Bit的片上ROM,包括64 k Bytes的DARAM(8塊,每塊4 kx16 Bit),192K Bytes的SARAM(24塊,每塊4 kxl6 Bit)。

4)64 k Bytes的一等待片上ROM(32 k×16 Bit)。

5)最大可尋址8 Mxl6 Bit的外部存儲空間。16位的外部存儲器擴展接口可實現與異步存儲器件(SRAM、EPROM)和同步存儲器件(SDRAM)的無縫連接。

6)片上外設包含:

2個20 Bit的定時器;

1個看門狗定時器;

1個六通道的直接存儲器訪問控制器(DMA);

1個主機接口(HPI);

3個多通道緩沖串行口(Mcbsp);

2個多媒體卡(MMC)或安全數字存儲卡(SD Card);

1個可編程的數字鎖相環時鐘發生器;

7個通用輸入輸出口(GPIO)和1個外部標志輸出引腳(XF);

1個通用串行USB接口(12 Mbps);

1個內部集成電路模塊(I2C);

1個實時時鐘(RTC);

1個兩通道的10Bit的逐次逼近式模數轉換器(ADC)。

7)JTAG仿真接口,符合IEEE1941.1標準(JTAG)邊界掃描邏輯。

1.5 A/D轉換器和CCD以及DSP的接口設計

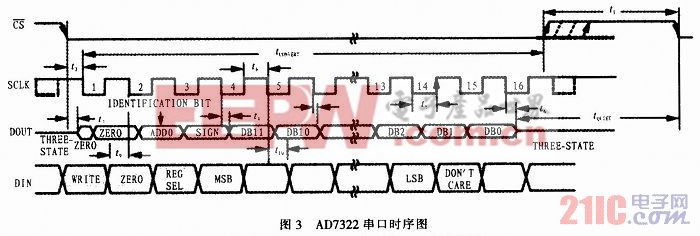

AD7322在數據轉換過程中,采用SCLK引腳上的串行時鐘用做轉換時鐘和控制從ADC中搬移數據的時鐘。的下降沿使得采樣與保持電路進入保持狀態并使總線為三態輸出,然后模擬輸入信號被采樣。一旦轉換開始,總共需要16個SCLK時鐘周期才能完成。在第14個SCLK的上升沿,采樣與保持電路回到跟蹤模式,在第16個SCLK的下降沿DOUT腳回到三態輸出狀態。如果經過16個SCLK時鐘周期,的上升沿到來,則轉換被中止,且DOUT腳回到三態輸出狀態。根據![]() 在什么時候信號的電平變高,被選擇的相應寄存器才有可能被更新。具體的串口時序如圖3所示。

在什么時候信號的電平變高,被選擇的相應寄存器才有可能被更新。具體的串口時序如圖3所示。

AD7322與CCD、DSP連接的原理框圖如圖4所示。

具體的連接方法是將CCD的行同步信號FC接入DSP的通用輸入輸出引腳GPI04腳。將CCD的像元同步信號SP接入DSP的McBSP幀同步輸入腳FSR,控制每一個像元的采樣與轉換。將DSP的幀同步輸出腳FSX腳接入AD7322的CS腳作為A/D芯片的選通信號。將DSP的McBSP的時鐘輸出腳CLKX和時鐘輸入腳CLKR接至AD7322的串行時鐘SCLK,保證A/D轉換器和McBSP工作在同一時鐘下。將CCD的模擬輸出信號U0經一個二階有源低通濾波電路濾波并經過一個雙運放OP2177進行驅動后的兩個輸出接入AD7322的兩個模擬輸入端VIN0和VIN1。將DSP的數據輸出引腳DX接入AD73 22的DIN引腳,作為對ADC的控制信號。將AD7322的輸出引腳D0與McBSP的數據輸入引腳DR相連。另外,本系統中的AD7322的參考電壓用的是ADC內部的參考電壓,所以需要在REFIN/OUT引腳要用一個680 nF的電容去耦到模擬地。

由于在信噪比和諧波失真有嚴格要求的情況下,AD7322的模擬輸入必須由一個低阻抗信源驅動,高阻抗信源很明顯地影響ADC的交流特性。所以本系統中采用一個雙運放OP2177,OP2177是ADI公司生產的高精度、低偏置、低功耗的集成運算放大器,片內集成了兩個運放,可靈活的組成各類放大和濾波電路。

評論