基于Matlab的FIR帶通濾波器設計及DSP實現(xiàn)

3 FIR數(shù)字帶通濾波器語音去噪的DSP實現(xiàn)

3.1 硬件結構

圖3為FIR帶通濾波器的語音去噪硬件結構框圖。系統(tǒng)主要由DSP芯片(TMS320C5402)、A/D轉換器(ADS7864)和D/A轉換器(DAC7625)組成。本文引用地址:http://www.104case.com/article/186064.htm

實現(xiàn)的核心器件采用TI公司生產(chǎn)的TMS320C5402芯片。該芯片采用先進的修正哈佛結構,片內(nèi)共有8條總線、CPU、在片存儲器、在片外圍電路等硬件和高度專業(yè)化的指令系統(tǒng),使它的處理速度和容量大大提高,為數(shù)字濾波中的復雜算法的實現(xiàn)提供了良好的保證。

A/D轉換器采用TI公司生產(chǎn)的ADS7864芯片,它是一個高速(轉換時間2μs)12位精度,6通道的A/D轉換器件。它的最高工作頻率可達8 MHz,采樣率為500 kHz。根據(jù)奈奎斯特定理,信號的最高頻率不能高于250 kHz,這樣才不會有失真,而這個頻率對于語音信號的處理已經(jīng)足夠。

D/A轉換芯片采用DAC7625,它是一個4路12位D/A轉換器件,每路都有輸入寄存器和DAC寄存器,構成雙緩沖結構,轉換時間為10μs。

3.2 軟件設計

3.2.1 數(shù)據(jù)組織方式

若輸入信號x(n)和濾波器的單位沖激響應h(n)在頻域分別為![]() ,則其輸出信號的頻率響應為

,則其輸出信號的頻率響應為![]() 。根據(jù)離散傅氏變換的性質(zhì),可以得到濾波系統(tǒng)的差分方程:

。根據(jù)離散傅氏變換的性質(zhì),可以得到濾波系統(tǒng)的差分方程:

![]()

從上文Matlab的仿真過程可得到濾波器的級數(shù)N和濾波器系數(shù)h(n)。從上述可知數(shù)字濾波器實現(xiàn)時,主要是進行乘和加運算以及數(shù)據(jù)存取操作。

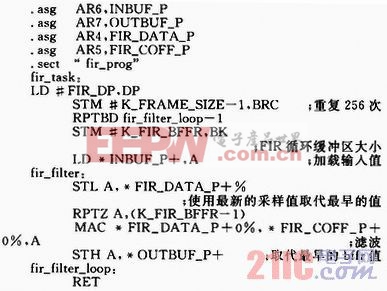

在定點DSP上實現(xiàn)FIR濾波有兩種方式:一種是用線性緩沖區(qū)實現(xiàn)z-1,該方式能保證新老數(shù)據(jù)在存儲器中的存放位置直接明了,新的數(shù)據(jù)存放在緩沖區(qū)的固定位置;另一種方式是循環(huán)緩沖區(qū)實現(xiàn)z-1,該方式新老數(shù)據(jù)在緩沖區(qū)的位置不直接明了,新的數(shù)據(jù)沒有固定位置,但可以方便地完成濾波器窗口的自動更新。考慮到本方案中使用的是匯編語言編程,還有N的階數(shù)較大,為提高速率,因此在選擇FIR濾波器的方式時選擇循環(huán)緩沖區(qū)實現(xiàn)z-1的方式。

對于N級的FIR濾波器,在數(shù)據(jù)存儲器中開辟一個稱之為滑窗的N個單元的緩沖區(qū),滑窗中存放最新的N個輸入樣本。每次輸入新的樣本時,一新樣本改滑窗中的最老數(shù)據(jù),而滑窗中的其他數(shù)據(jù)不需要移動。利用片內(nèi)BK(循環(huán)緩沖區(qū)長度)寄存器對滑窗進行間接尋址,環(huán)緩沖區(qū)地址首位相鄰。

3.2.2 程序設計思路

程序設計的總體思路是:啟動ADS7864對輸入的模擬信號進行A/D轉換,每采集到一個數(shù)據(jù)就送入DSP進行濾波運算,運算結果送DAC76 25轉換為模擬量。不斷地重復上述過程,在DAC7625的輸出端就得到濾波后的模擬信號。

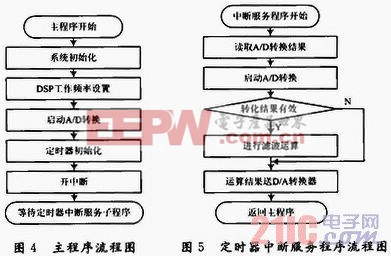

為了精確地控制ADS7864的采樣率,使用TMS320C5402內(nèi)部的定時器控制采樣時間間隔T。設置定時器的定時時間等于采樣時間間隔T,并讓它工作在中斷方式,則定時器每過T時間間隔就向CPU發(fā)出中斷請求,CPU響應中斷請求,轉去執(zhí)行中斷服務程序。在中斷服務程序中讀取A/D轉換結果,對轉換結果進行濾波運算,并將運算結果送D/A轉換器轉換為模擬量。因此,程序分為主程序和定時器中斷服務程序兩部分,流程圖如圖4,圖5所示。

3.2.3 FIR濾波源程序

FIR濾波器指令,使用MAC指令執(zhí)行FIR濾波,將濾波輸出放在累加器A中:

評論