全同步數字頻率計的 VHDL設計與仿真

1 引 言

頻率測量不僅在工程應用中有非常重要的意義,而且在高精度定時系統中也處于核心地位,±1個計數誤差通常是限制頻率測量精度進 一步提高的重要原因。由于測頻技術的重要性,使測頻方法也有了很大的發展,常用數字頻率測量方法有M法,T法,和M/T(等精度測量法)法。M法,T法, 和M/T法都存在±1個計數誤差問題:M法存在被測閘門內±1個被測信號的脈沖個數誤差,T法或M/T法也存在±1個字的計時誤差,這個問題成為限制測量 精度提高的一個重要的原因。全同步頻率測量法[1],從根本上消除了限制測量精度提高的±1個計數誤差問題,從而使頻率測量的精度和性能大為改善。

基于對FPGA器件和EDA技術以及全同步測頻方法的研究[2,3],介紹一種利用FPGA實現DC~100 MHz全同步數字頻率計的實現方法,并給出VHDL實現代碼和仿真波形。整個系統在研制的FPGA/CPID實驗開發系統上調試通過。本設計采用了高集成度的現場可編程門陣列(Field Program-mable Gata Array,FPGA)Flex EPF10k20TCl44-4芯片[4],通過軟件編程對目標器件的結構和工作方式進行重構,能隨時對設計進行調整,使得本設計具有集成度高、結構靈活、開發周期短、可靠性高的優點。

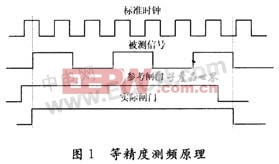

在文獻[2,5]中所描述的等精度頻率測量方法中,其測頻原理如圖1所示。

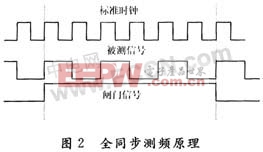

其 誤差與閘門時間和標準時鐘頻率有關,閘門時間越長,標準時鐘頻率越高,誤差越小。因此,用等精度測頻法時所取的標準時鐘頻率比較高(10 MHz以上),因此±1計數誤差相對很小。標準時鐘頻率不可能無限制提高,并且隨著頻率提高,產品成本成倍增加,對于生產應用沒有意義。因此本設計用改進 的等精度頻率測量方法--全同步測量來實現數字頻率計的設計。在全同步的情況下,閘門信號不僅與被測信號同步,還與標準時鐘同步。其原理圖如圖2所示。

2 全同步測頻原理簡述

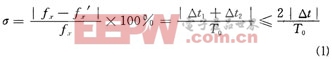

由文獻[1,6]可知:設開啟閘門時脈沖同步時間差為△t1,關閉閘門時脈沖同步時間差為△t2,脈沖同步檢測最大誤差為△t,則有:△t1≤△t,△t2≤△t。頻率測量的相

對誤差如式(2)所示:

由式(1)可知,誤差只與脈沖檢測電路準確度有關,顯然,控制△t來提高頻率測量精度是有效的,而且實現走來比提高標準時鐘頻率更容易。

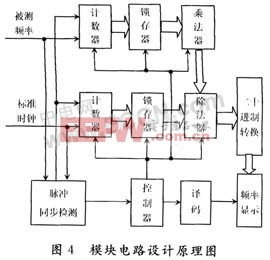

在以上分析的基礎上,本設計采用FPGA來實現全同步數字頻率計。其系統原理框圖如圖3所示。由圖3可知,設計的絕大部分由FPGA完成,只有脈沖同步檢測電路由74LS系列與非門來實現,以及顯示部分由數碼管構成。

3 全同步數字頻率計模塊設計

由系統原理框圖3,則其FPGA內部模塊電路設計原理如圖4所示。

設 計原理圖主要由以下幾部分組成:脈沖同步檢測電路、2個計數器、2個鎖存器、控制器、乘法器、除法器、澤碼電路等組成。工作原理如下:被測頻率與標準時鐘 分別送給脈沖同步檢測電路與2個計數器,當脈沖同步檢測電路檢測到被測頻率與標準時鐘相位同步時,脈沖同步檢測電路發出同步信號,2個計數器開始計數,當 脈沖同步檢測電路再次檢測到間步信號時,義發出同步信號,計數器停止計數。同時計數器的計數值鎖存到鎖存器,時序乘法器從鎖存器中取得被測頻率的計數值與 標準時鐘頻率進行乘法運算,然后再將乘法器運算所得的值與標準時鐘的計數值送給除法器,乘法器的結果為被除數,標準時鐘的計數值為除數,運算所得結果就是 被測信號的頻率,然后冉經過二卜進制轉換變成BCD碼,送給數碼管顯示。本設計采用10 MHz的標準時鐘,由于乘法器輸入是27位二進制,相當于9位10進制數,而10 MHz的標準時鐘為107Hz,因此用被測頻率的計數值乘以108可得到一位小數點。

3.1 脈沖同步檢測電路

脈沖同步檢測電路 沒計原理圖如圖5所示。U1~U8為74LS系列與非門,同步檢測電路利用門電路的延時來構成。當被測信號及標準時鐘都處在低電平時,U1,U2輸出為高 電平,U3,U4的輸出為高電平,U5,U6輸出為低電平,則U8輸出為低電平。當被測信號(Fx)及標準時鐘的上升沿同時到來時,由于門電路具有延時特 性,因此U1,U2并不馬上變為低電平,而是要經過一個延時才變為低電平。于是U3,U4的輸入端都是高電平,則U3,U4

輸出為低電平,U5,U6的輸出為高電平,則U8輸出為高電平。但是當且儀當Fx與CLK的上升沿在在延時時間內同時到達時U8才會輸出高電平。74LS系列與非門的延時最小為4 ns,最大為15 ns,因此最大誤差為11ns。根據公式(2)得:![]()

當T0為1 s時,其精度可達到10-7,如再減小相位誤差,則可提高頻率計的精確度。

評論