放大器電路設(shè)計(jì)關(guān)鍵事項(xiàng)精華匯總(二)

正確地提供儀表放大器的參考電壓

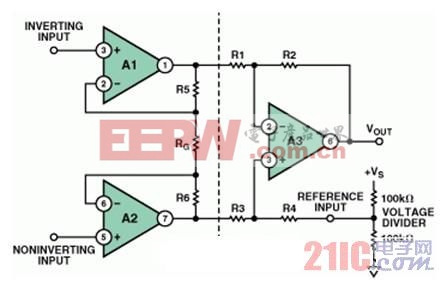

本文引用地址:http://www.104case.com/article/185952.htm一般假設(shè)儀表放大器的參考輸入端為高阻抗,因?yàn)樗且粋€(gè)輸入端。所以使設(shè)計(jì)工程師一般總想在儀表放大器的參考端引腳接入一個(gè)高阻抗源,例如一只電阻分壓器。這在某些類型儀表放大器的使用中會(huì)產(chǎn)生嚴(yán)重誤差(見圖8)。

圖8. 錯(cuò)誤地使用一個(gè)簡(jiǎn)單的電阻分壓器直接驅(qū)動(dòng)3運(yùn)放儀表放大器的參考電壓引腳

例如,流行的儀表放大器設(shè)計(jì)配置使用上圖所示的三運(yùn)放結(jié)構(gòu)。其信號(hào)總增益為

參考電壓輸入端的增益為1(如果從低阻抗電壓源輸入)。但是,在上圖所示的電路中,儀表放大器的參考輸入端引腳直接與一個(gè)簡(jiǎn)單的分壓器相連。這會(huì)改變減法器電路的對(duì)稱性和分壓器的分壓比。這還會(huì)降低儀表放大器的共模抑制比及其增益精度。然而,如果接入R4, 那么該電阻的等效電阻會(huì)變小,減小的電阻值等于從分壓器的兩個(gè)并聯(lián)支路看過(guò)去的阻值(50 kΩ),該電路表現(xiàn)為一個(gè)大小為電源電壓一半的低阻抗電壓源被加在原值R4上,減法器電路的精度保持不變。

如果儀表放大器采用封閉的單封裝形式(一個(gè)IC),則不能使用這種方法。此外,還要考慮分壓電阻器的溫度系數(shù)應(yīng)該與R4和減法器中的電阻器保持一致。最終,參考電壓將不可調(diào)。另一方面,如果嘗試減小分壓電阻器的阻值使增加的電阻大小可忽略,這樣會(huì)增大電源電流的消耗和電路的功耗。在任何情況下,這種笨拙的方法都不是好的設(shè)計(jì)方案。

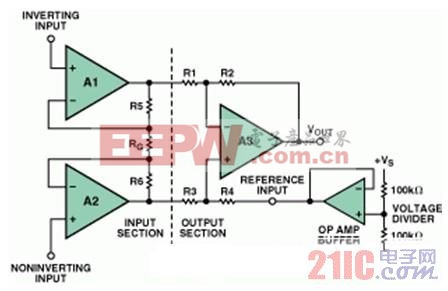

圖9示出了一個(gè)更好的解決方案,在分壓器和儀表放大器參考電壓輸入端之間加一個(gè)低功耗運(yùn)算放大器緩沖器。這會(huì)消除阻抗匹配和溫度系數(shù)匹配的問題,而且很容易對(duì)參考電壓進(jìn)行調(diào)節(jié)。

圖9. 利用低輸出阻抗運(yùn)算放大器驅(qū)動(dòng)儀表放大器的參考電壓輸入端

當(dāng)從電源電壓利用分壓器為放大器提供參考電壓時(shí)應(yīng)保證PSR性能

一個(gè)經(jīng)常忽視的問題是電源電壓VS的任何噪聲、瞬變或漂移都會(huì)通過(guò)參考輸入按照分壓比經(jīng)過(guò)衰減后直接加在輸出端。實(shí)際的解決方案包括旁路濾波以及甚至使用精密參考電壓IC產(chǎn)生的參考電壓,例如ADR121,代替VS分壓。

當(dāng)設(shè)計(jì)帶有儀表放大器和運(yùn)算放大器的電路時(shí),這方面的考慮很重要。電源電壓抑制技術(shù)用來(lái)隔離放大器免受其電源電壓中的交流聲、噪聲和任何瞬態(tài)電壓變化的影響。這是非常重要的,因?yàn)樵S多實(shí)際電路都包含、連接著或存在于只能提供非理想的電源電壓的環(huán)境之中。另外電力線中的交流信號(hào)會(huì)反饋到電路中被放大,而且在適當(dāng)?shù)臈l件下會(huì)引起寄生振蕩。

現(xiàn)代的運(yùn)算放大器和儀表放大器都提供頻率相當(dāng)?shù)偷碾娫措妷阂种?PSR)能力作為其設(shè)計(jì)的一部分。這在大多數(shù)工程師看來(lái)是理所當(dāng)然的。許多現(xiàn)代的運(yùn)算放大器和儀表放大器的PSR指標(biāo)在80~100dB以上,可以將電源電壓的變化影響衰減到1/10,000~1/100,000。甚至最適度的40 dB PSR的放大器隔離對(duì)電源也可以起到1/100的抑制作用。不過(guò),總是需要高頻旁路電容(正如圖1~7所示)并且經(jīng)常起到重要作用。

此外,當(dāng)設(shè)計(jì)工程師采用簡(jiǎn)單的電源電壓電阻分壓器并且用一只運(yùn)算放大器緩沖器為儀表放大器提供參考電壓時(shí),電源電壓中的任何變化都會(huì)通過(guò)該電路不經(jīng)衰減直接進(jìn)入儀表放大器的輸出級(jí)。因此,除非提供低通濾波器,否則IC通常優(yōu)良的PSR性能會(huì)丟失。

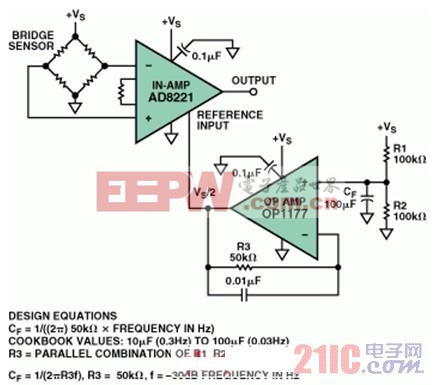

在圖10中,在分壓器的輸出端增加一個(gè)大電容器以濾除電源電壓的變化并且保證PSR性能。濾波器的-3 dB極點(diǎn)由電阻器 R1/R2并聯(lián)和電容器C1決定。-3 dB極點(diǎn)應(yīng)當(dāng)設(shè)置在最低有用頻率的1/10處。

圖10. 保證PSR性能的參考端退耦電路

上面示出的CF試用值能夠提供大約0.03 Hz的-3 dB極點(diǎn)頻率。接在R3兩端的小電容器(0.01 µF)可使電阻器噪聲最小。

該濾波器充電需要時(shí)間。按照試用值,參考輸入的上升時(shí)間應(yīng)是時(shí)間常數(shù)的幾倍(這里T = R3Cf = 5 s),或10~15s。

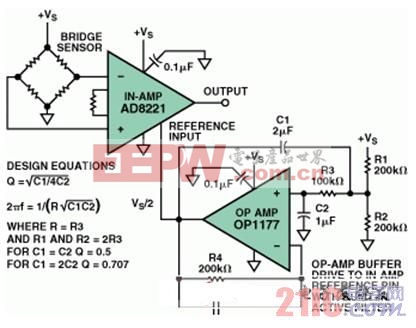

圖11中的電路做了進(jìn)一步改進(jìn)。這里,運(yùn)算放大器緩沖器起到一個(gè)有源濾波器的作用,它允許使用電容值小很多的電容器對(duì)同樣大的電源退耦。此外,有源濾波器可以用來(lái)提高Q值從而加快導(dǎo)通時(shí)間。

圖11. 將運(yùn)算放大器緩沖器接成有源濾波器驅(qū)動(dòng)儀表放大器的參考輸入引腳

測(cè)試結(jié)果:利用上圖所示的元件值,施加12 V電源電壓,對(duì)儀表放大器的6 V參考電壓提供濾波。將儀表放大器的增益設(shè)置為1,采用頻率變化的1 VP-P正弦信號(hào)調(diào)制12 V電源。在這樣的條件下,隨著頻率的減小,一直減到大約8 Hz時(shí),我們?cè)谑静ㄆ魃峡床坏紸C信號(hào)。當(dāng)對(duì)儀表放大器施加低幅度輸入信號(hào)時(shí),該電路的測(cè)試電源電壓范圍是4 V到25 V以上。電路的導(dǎo)通時(shí)間大約為2 s。

單電源運(yùn)算放大器電路的退耦

最后,單電源運(yùn)算放大器電路需要偏置共模輸入電壓幅度以控制AC信號(hào)的正向擺幅和負(fù)向擺幅。當(dāng)從電源電壓利用分壓器提供偏置電壓時(shí),為了保證PSR的性能就需要合適的退耦。

一種常用但不正確的方法是利用100 kΩ/100 kΩ電阻分壓器(加0.1µF旁路電容)提供VS/2給運(yùn)算放大器的同相輸入端。使用這樣小的電容值對(duì)電源退耦通常是不夠的,因?yàn)闃O點(diǎn)僅為32 Hz。電路出現(xiàn)不穩(wěn)定(“低頻振蕩”),特別是在驅(qū)動(dòng)感性負(fù)載時(shí)。

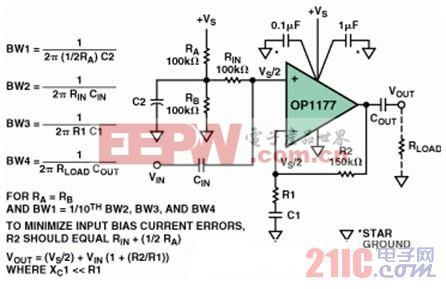

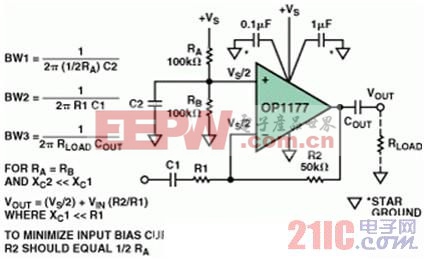

圖12(反相輸入)和圖13(同相輸入)示出了達(dá)到最佳退耦結(jié)果的VS/2偏置電路。在兩種情況中,偏置電壓加在同相輸入端,反饋到反向輸入端以保證相同的偏置電壓,并且單位DC增益也要偏置相同的輸出電壓。耦合電容器C1使低頻增益從BW3降到單位增益。

圖12. 單電源同相輸入放大器電路正確的電源退耦方案。中頻增益=1+R2/R1

如上圖所示,當(dāng)采用100 kΩ/100 kΩ電阻分壓器時(shí)一個(gè)好的經(jīng)驗(yàn)是,為獲得0.3 Hz的 - 3 dB截止頻率,應(yīng)當(dāng)選用的C2最小為10 µF。而100 µF(0.03 Hz)實(shí)際上對(duì)所有電路都足夠了。

圖13. 單電源反相輸入放大器正確的退耦電路

中頻增益= - R2/R1

更多資訊請(qǐng)關(guān)注:21ic模擬頻道

評(píng)論