基于預失真技術(shù)的短波功率放大器線性化系統(tǒng)

摘 要:本文提出了一種基于預失真技術(shù)的短波功率放大器線性化系統(tǒng)的設(shè)計方案,該方案采用查找表技術(shù),且使用了一種獨特的放大特性測量方法,具有很強的實用性。

關(guān)鍵詞:預失真;功放線性化;查找表

引言

隨著通信技術(shù)的發(fā)展,線性調(diào)制技術(shù)和寬帶通信技術(shù)正得到越來越廣泛的應(yīng)用。在多通道短波通信發(fā)射設(shè)備中,多個包絡(luò)變化很大的單邊帶調(diào)制信號經(jīng)過疊加后,形成的寬帶信號通過非線性射頻功率放大器后會產(chǎn)生交調(diào)分量,因此,必須采用線性化技術(shù)以減少由此,產(chǎn)生的鄰道干擾。預失真技術(shù)是一種廣泛應(yīng)用的線性化技術(shù),其優(yōu)點是方法靈活,相對復雜度較低。

系統(tǒng)結(jié)構(gòu)

對于短波通信而言,由于大多采用的是多載波單邊帶調(diào)制技術(shù),信號對幅度敏感,而對相位不敏感,因此本文的假設(shè)前提是信號本身對相位不敏感,在此基礎(chǔ)上提出以下方法。

本文的預失真器是以查找表為基礎(chǔ)的,其結(jié)構(gòu)如圖1所示。首先,根據(jù)功放特性測量的結(jié)果,按照某種算法建立預失真系數(shù)表。工作時,由輸入信號的幅度產(chǎn)生查找表的地址(因為功放特性一般為信號幅度值的函數(shù)),并由此產(chǎn)生預失真系數(shù),輸入信號與該系數(shù)相乘,得到預失真信號。

圖1 預失真器的結(jié)構(gòu)

預失真技術(shù)的關(guān)鍵

查找表的建立

設(shè)理想功放的放大率為K,對應(yīng)于信號xn的功放的放大系數(shù)為gn,預失真器的系數(shù)為fn。yn=Kxn為理想放大器對應(yīng)于xn的響應(yīng)。通過測量的功放特性曲線表,可以查到當輸出幅度ym=yn時對應(yīng)的輸入xm,從而得到以下關(guān)系:xmgm=Kxn=yn

若xn預失真后的信號滿足xnfn=xm,則xnfngm=Kxn

從而,系統(tǒng)滿足理想功放的特征。

因此,預失真系數(shù)可由下式計算得到:fn=xm/xn。

預失真系數(shù)表的創(chuàng)建過程為:根據(jù)輸入信號xn,計算其理想的響應(yīng)yn,然后,通過功放特性表查找對應(yīng)于響應(yīng)yn的輸入信號xm,最后計算預失真系數(shù)fn=xm/xn。

功放特性的測量

對功率放大器非線性特性進行測定時,其輸出信號為一個具有非線性失真的正弦信號,其中心頻率設(shè)為f0。當然,它不是一個單一頻率的信號。對功放輸出信號不能進行窄帶濾波,否則就測不到其非線性失真特性。其次,也不能采用模擬幅度檢波的辦法來測定其幅度,因為模擬檢波器的效果不夠理想。

對功放輸出的信號只能通過A/D轉(zhuǎn)換,來測定功放失真特性參數(shù),即其輸出信號最大值。

對功放失真特性的測量,具有兩個特點:一是其中心頻率可以選定,大概在10MHz~15MHz之間;二是只需測得其最大值。最大值不能通過積累或濾波的方法得到,因為功放輸出的是失真的正弦信號,對它進行信號處理會引起失真。

設(shè)采樣率足夠高,通過計算機模擬,得到ADC精度b=14和b=16時的兩組曲線(見圖2),其它參數(shù)相同。

圖2 預失真系統(tǒng)仿真結(jié)果

可見,測量精度對預失真處理效果十分明顯,b=16時噪聲電平較b=14時小6dB。

受器件限制,當ADC精度較高時,其采樣率不易做高。

為敘述方便,設(shè)功放輸出為y(t)=cos(2f0t)。

測定y(t)的最大值時,由于采樣率的原因,最大可能的誤差為error=

為充分利用ADC的精度,要求error<1/2b-1,即1-cos(?f0 / fs)<1/2b-1

當b=16,f0=11MHz時,其相位偏差小于0.0087弧度(即0.5),則fs>4400MHz

這說明,如果對一個正弦信號的一個周期進行采樣,那么采樣率要高于4400MHz,才能保證采集到最大值。這顯然不現(xiàn)實。實際上可以較低的采樣速率對信號的多個周期進行連續(xù)采樣,以達到同樣的效果。

設(shè)y(n)=cos(2f0n/fs),若fs為f0的整數(shù)倍M,則y(n)=cos(2n/M),

每個周期采集到的信號樣點都是相同的,能否采集到信號的最大值取決于開始采樣的時刻。因此,這種情況是達不到目的的。

若fs不為f0的整數(shù)倍,設(shè)fs/f0=M+p/q,其中M為整數(shù),p、q為互素的整數(shù),且p q,則有y(n)=cos(2n/(M+p/q))=cos(2qn/(qM+p))

在這種情況下,0 n N,其中N=qM+p,在連續(xù)q個周期內(nèi)采樣,得到N個不同相位的樣點,這等價于以更高的采樣速率在一個周期內(nèi)采樣N個點。

若相鄰采樣點間的相位差小于0.5,則360/N 0.5,即N 720。

在設(shè)計中,通常先確定M和連續(xù)采樣的周期數(shù)q,最后確定p。

取采樣率fs=160/3MHz,由于f0一般在10MHz~15MHz之間,所以可取M=3~5。這里取M=5,q=144, 在此情況下p可取1,5,7,11,…143,這里取p=43,得到的f0為10.0655MHz。

仿真發(fā)現(xiàn),采樣點中數(shù)值≥cos(0.5?=0.9996的點有兩個,即239和594,從而可知結(jié)論是正確的。

理論上,采集到最大值所需時間為N/fs=(qM+p)/(160/3)ms=14.3062ms。實際中,需要采樣的時間要遠大于這個值,這里取t=20(N/fs)=286.124≈287ms。

注意,在287ms期間內(nèi),可以得到一個正的最大值和一個負的最大值,應(yīng)根據(jù)實際情況選其中之一或從兩者取其一折衷。

以較低的采樣速率對信號進行多周期連續(xù)采樣,可得到以較高速率對單個周期采樣的效果。這種方法解決了ADC器件的選型問題。

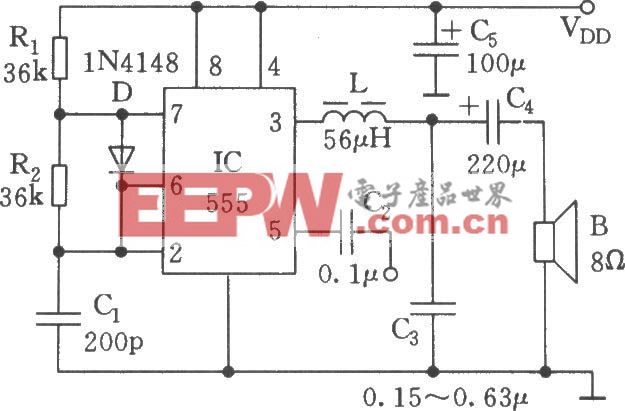

圖3 系統(tǒng)設(shè)計原理圖

系統(tǒng)設(shè)計

本文所設(shè)計的系統(tǒng)如圖3所示。

時鐘分配:DSP時鐘由專用的10MHz晶振提供;其他時鐘由40MHz的晶振時鐘通過CPLD和FPGA提供:40MHz一路進入CPLD,經(jīng)過4分頻后輸出,作為AD73322的主時鐘,另一路進入FPGA,經(jīng)過內(nèi)部PLL倍頻和分頻,產(chǎn)生80MHz、160MHz、160/3MHz的時鐘,分別送入ISL5217、AD9777和AD9244。

各器件的主要參數(shù)配置

AD73322:DMCLK=輸入時鐘=1,采樣速率為DMCLK/256=39.0625KHz,SCLK=DMCLK/8。

ISL5217:載頻為10.0655MHz,載頻相位=0,采樣頻率為39.0625KHz,插值倍數(shù)=16,數(shù)據(jù)輸入方式為并口,數(shù)據(jù)輸出方式為real、Shaping Filter 系數(shù)設(shè)置等。

AD9777:內(nèi)插倍數(shù)=2,調(diào)試方式為none,雙端口輸入模式,使能PLL。

FPGA的主要工作:控制模塊,2倍插值濾波器,查找表,A/D采樣最值的搜索。

系統(tǒng)任務(wù)

前向通路:兩個任務(wù),一是發(fā)送測試數(shù)據(jù)到功放并輸出;二是正常的數(shù)據(jù)通路。ADC以39.0625KHz的速率采樣數(shù)據(jù),然后將數(shù)據(jù)傳送到DSP處理。DSP經(jīng)過AGC、濾波和調(diào)制后,以39.0625KHz的速率傳送到上變頻器ISL5217,它將對輸入數(shù)據(jù)進行2048倍插值,達到80MHz,然后將其調(diào)制到10.0655MHz的載頻上,送往FPGA。FPGA將對其再進行2倍插值處理,然后進行預失真。最后,F(xiàn)PGA將預失真的數(shù)據(jù)送入DAC。DAC將對數(shù)據(jù)進行2倍插值處理,數(shù)據(jù)速率達到320MHz,然后經(jīng)DAC輸出到功放。

反饋通路:負責功放特性的測量。RF_DA將以160/3MHz的速率進行采樣,采樣后的數(shù)據(jù)進入FPGA,F(xiàn)PGA將檢測這些采樣數(shù)據(jù)幅度最大值(正和負),并將其送到DSP進行記錄。

系統(tǒng)工作流程

器件配置

在系統(tǒng)調(diào)試完成后,首先在CCS環(huán)境下將FPGA加載文件燒寫到Flash存儲器中(只燒寫一次),在以后的工作中,開機后,由DSP程序?qū)PGA的加載文件從Flash存儲器讀出來,通過FPGA串行配置方式加載到FPGA上,這樣,其他芯片就有了時鐘,然后DSP再配置其他器件。

功放特性的測量

DSP以39.0625KHz發(fā)數(shù)據(jù),從0到最大值32767,每個數(shù)據(jù)發(fā)送時間持續(xù)287ms,產(chǎn)生幅度恒定的正弦波,然后從FPGA中讀取相應(yīng)的包絡(luò)幅度最值。注意,在搜索最值前,應(yīng)先使發(fā)送信號穩(wěn)定下來,以確保檢測到的信號的準確性。

查找表的建立

考慮到采樣的誤差,檢測到的信號并不是平滑的曲線,如果直接利用監(jiān)測到的信號來建表,系統(tǒng)誤差是很大的。因此,要對采樣的信號進行平滑處理,其方法是多樣的,這里不作說明。由于采樣信號的范圍可能小于-32767~+32767,要做歸一化處理,最后是啟動正常的工作順序。

結(jié)語

預失真是實現(xiàn)功率放大器線性化的有效方法,其實現(xiàn)簡單易行,系統(tǒng)穩(wěn)定。本文提出的方法簡單有效,非常適用于一次開機后,使用時間比較短的應(yīng)用,因為時間長,系統(tǒng)溫度會發(fā)生變化,功放的溫漂會造成功放特性的顯著變化,使系統(tǒng)性能極度惡化。

參考文獻

1.趙洪新,陳憶元,洪偉.一種基帶預失真RF功率放大器線性化技術(shù)的模型仿真和實驗,通信學報,2005年5月,第五期,第21卷

2.Intersil com,AN1022, Operation and Performance of the ISL5239 Pre-distortion Linearizer,July 2002

評論