一個高性能帶隙基準電壓源的設計

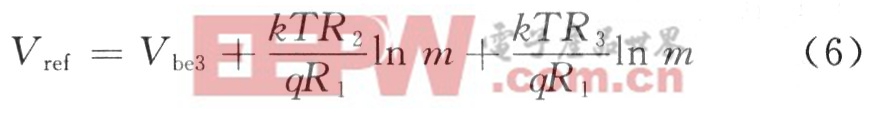

由文獻[2]可知,二次曲率的校正可以通過不同溫度系數的電阻來實現,即:

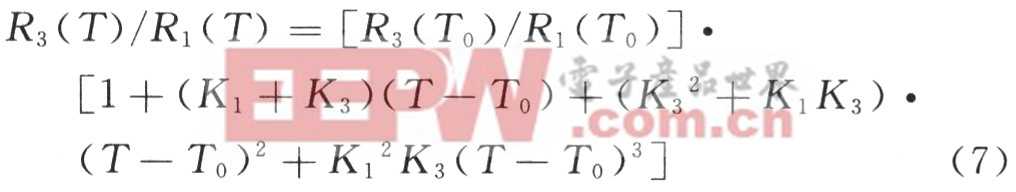

由于R1和R3具有不同的溫度系數,對二者比值用泰勒公式展開,有:

式中:K1為R1的溫度系數,為正值;K3為R3的溫度系數,為負值。二者的溫度系數正負差異越大,曲率補償的效果就越好。

當MOS管的柵一源電壓接近于開啟電壓時,該MOS管就工作在亞閾值區。此時,流過管子的電流與柵一源電壓呈指數關系,其電流公式如下:

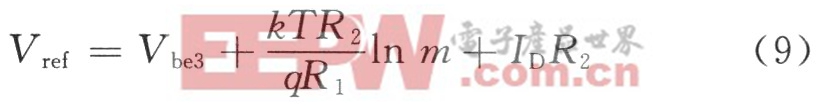

式中:n為亞閾值斜率因子(1n3);ID0是一個與工藝有關的參數。由圖2可知,由于流過M19的電流與M15,M17的電流相等,則有:

![]()

由式(4)、式(6)~式(8)整理得:

![]()

由于m1/n>1,所以R3和R2的溫度系數差異得到了指數關系的放大,從而對Vbe3的二階溫度系數有了更好的補償效果,而且該特性只需要1個N型MOS管實現,相對于文獻[3]來說,節省了電阻的占用面積,很適合在工程上使用。

1.3 提高電源抑制電路與啟動電路分析

原則上來說,傳統的帶隙電路本身具有較好的電源抑制特性,其輸出電壓幾乎與電源電壓無關,但是目前工程上使用的MOS管大部分為亞微米器件,因而不可避免地產生二級效應(主要是溝道長度調制效應和體效應),對流過MOS管的電流I產生影響。所以要得到一個精準的基準電壓,必須引入額外電路,提高電路的電源電壓抑制能力。

在該設計中,除了采用cascode結構外,額外增加了M21~M28來實現對電源波動的抑制,如圖2所示。帶隙的核心電路電壓由V1提供,當電源電壓 VDD升高時,V1電平也將升高,同時由M21~M24感應運放兩個輸入節點電位差并將其進一步放大,提升了M25的柵極電位,同時通過M26鏡相電流的增大,使流過M25的電流增大,降低了M25的等效輸出電阻,最終使V1電平降低。顯然放大器的增益越高,對電源波動的抑制越好。

由于電路存在兩個偏置點,為了保證電路的正常工作,加入了M29~M31的啟動電路。當電源電壓接通時,可能出現各支路電流為零的情況,電路處于非正常工作狀態,此時輸出電壓也為0。由于M30和M31組成的反相器使M29的柵極電位變為高,故M29將導通并向電路注入電流,使電路啟動恢復正常工作狀態,此時電路輸出電壓為高,M29柵極電位變為0,M29關斷,所以對電路正常工作不會產生影響。電路中pwr主要控制電路的開關狀態,當pwr接高/低電平時,電路處于關/開狀態。

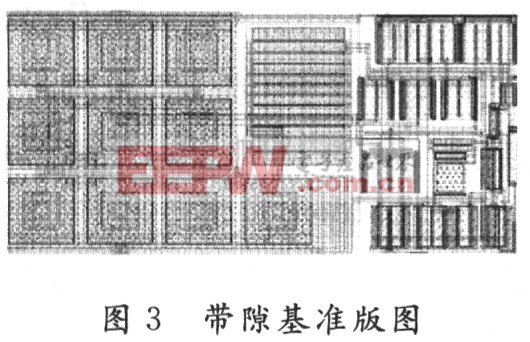

2 版圖設計

最終版圖設計如圖3所示,在該設計中版圖設計需要注意的主要問題是保證器件之間的匹配和對稱,匹配的器件布局要緊湊,并盡可能保證周圍環境的一致性,例如,運放的輸入差分對M8和M9、同材料電阻R1和R2等。因為運放的失調對電路的性能影響較大。而電阻的失配也會對輸出電壓的溫度特性產生影響。另外,構成電流鏡的MOS管之間保持對稱性在該設計中也是至關重要的。為了抑制溝道長度調制效應,在該設計中, MOS管的溝道長度取工藝允許的最小長度的兩倍。最后,在面積和性能之間取一個折衷關系,將Q1與Q2的面積之比定為8:1。

3 后仿真模擬結果

該電路設計主要采用TSMC CMOS 0.18/μm工藝,使用Cadence Spectre進行仿真,并用calibre完成版圖的參數提取。

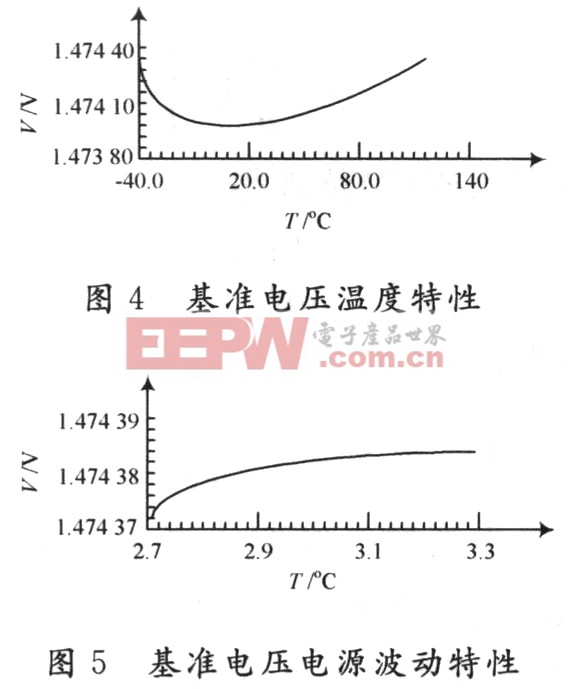

后仿真輸出電壓隨溫度的變化如圖4所示。從圖中可以看到,在溫度-40~+120℃范圍內,電壓僅變化O.39 mV,溫度系數約為3.3 ppm/℃。基準電壓隨電源電壓的變化如圖5所示。電源電壓從2.7~3.3 V變化范圍內,輸出的基準電壓變化在18μV左右。

4 結 語

采用0.18μm標準CMOS工藝設計了一個應用于高精度要求場合的基準電壓源,采用一種新的二階補償方法對傳統帶隙進行了改進,并加入反饋電路來提高電路的電源電壓抑制特性。結果表明,輸出電壓的溫度系數僅為3.3 ppm/℃,在電源電壓2.7~3.3 V波動范圍內,輸出電壓波動為18μV,而且電路的二階補償部分僅用了3個器件,節省了設計面積,很適合實際工程的使用,具有很大的實用價值。

評論