電源管理子系統IC及其應用

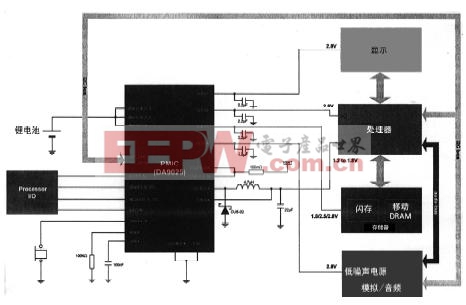

典型系統中的PMIC示于圖2,需要注意幾個不同的外部問題。例如,電源管理需要直接與電池(一般是單個鋰離子電源)接口,而工作時有沒有控制器產生和控制若干系統電源。在最簡單的系統(沒有控制器,但需要多個電源)中,加一個合適的電池電壓和使能信號將啟動器件,激勵所有的穩壓器。PMIC可以繼續工作,直到用戶用ONKEY引腳關斷器件或發生錯誤條件為止(如低電池電壓)。

從控制和可編程性觀點看,關于穩定輸出電壓的選擇越多,靈活性就越大。通過專門引腳,用簡單控制接口到微控制器是一種簡單的選擇,通過I2C總線用更全面地控制,可以提供可編程輸出電壓。

通常,PMIC包含若干LDO穩壓器、DC-DC降壓轉換器和其他功能。

LDO電壓穩壓器是電源管理系統的中心部分,能為系統中其他IC產生穩定、低噪聲電源電壓。LDO的重要性能參量是電源抑制比(PSRR)和靜態電流,后者將直接影響待機時間。每個穩壓器的靜態電流似乎是小的,但系統中有多個穩壓器和其他功能加起來會增大10或20倍,這會變得很大。

PSRR是干擾電平的量測,一旦發生穩壓,PSRR仍然呈現在電源線上。若這種瞬態不能被抑制,則它們會呈現在音頻頻段,成為不舒服的音調。另外的情況是會添加對RF信號的調制,這可能導致假的傳輸,而需要另外的濾波來去除它們。

為了在寬頻段達到高PSRR,LDO誤差放大器通常具有偏置電流校準,用于最壞工作條件下校準最高輸出電流。隨著偏置的固定和與電流定位無關,這會導致放大器過偏置和消耗比低電流定值所要求的更高靜態電流。基于此原因,高性能LDO設計通常需要有低功率休眠模式,以降低低電流定值下的低效率。

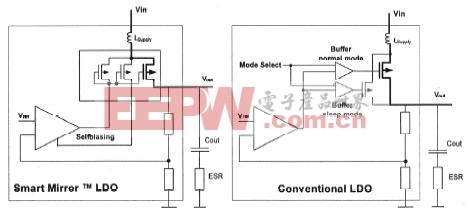

Dialog Semiconductor 公司的專利是解決此問題的獨特方法,是采用稱之為Smart Mirror LDO穩壓器的設計技術,這種穩壓器比當今所用的其他穩壓器具有更佳的PSRR性能。

Smart Mirror 穩壓器鏡像返回到偏置產生器的輸出電流定值,使偏置隨定值下降而自動降低并給出動態的靜態電流控制(見圖3)。這種方法所設計的穩壓器在寬工作電流范圍具有高PSRR和動態性能,這不受所有條件(最大負載除外)下過偏置設計折衷考慮的限制。具有自動自適應偏置控制,消除了所需的低功率工作模式和任何用戶干預開關到低電流定值的低功率模式。

采用此技術提供10mA的LDO通常具有99%電流效率,耗電低于20μA。另外,電源抑制在較高帶寬(217Hz)下具有較高性能。

評論