用于時間交織ADC的高精度開環跟蹤保持電路設計

圖2給出了本文所采用的自舉采樣開關的結構。該電路主要包括時鐘自舉和柵壓自舉NMOS開關兩部分。其中M1~M2和C1~C2組成時鐘自舉電路,M3~M4和CB組成柵壓自舉電路。整個電路由兩相不交疊時鐘控制。

當時鐘CLK為高時,M6~M7導通可將開關MS柵壓拉到地,同時M3~M4眠管導通可對CB進行充電至Vdd;反之,當時鐘CLK為低時,CB放電,M8管導通,輸入信號電壓VIN加到CB下極板上,開關管MS的柵極電壓被提高到(VIN+Vdd),從而使開關管的柵源電壓恒定為Vdd。

由于傳統的柵壓自舉電路中,電容CB上下極板相連的寄生電容會導致電荷共享,從而使開關的柵源電壓減小。

其中,CP表示與充電電容CB相連的寄生電容的總和。電容C3的加入不僅可以加速M9管迅速導通,而且更重要的是降低了電路的寄生電容,減小了對輸入信號造成的影響,從而提高開關MS的柵源電壓,改善開關的線性度。M1~M4的尺寸可以適當大些,以加快充放電速度,另外,下拉開關M2也可以適當大些,以加速關斷。溝道電荷注入也是影響開關線性度的另一個重要因素,因此,本設計加入了冗余開關管MD,以降低溝道電荷注入,改善開關的性能。

3 緩沖器設計

緩沖器作為TH電路設計的另一個重要部分,其增益和帶寬都將影響整個ADC的動態性能。在以往的開環結構中,緩沖器的結構主要有源級跟隨器(SF)和單位增益放大器兩種形式。SF的設計結構簡單且功耗較低。理想的SF具有較好的線性度和單位增益放大能力且此性能與偏置電流和晶體管尺寸都不相關。然而,在實際運用中,SF會受到體效應和短溝效應的影響,從而導致信號衰減和增益的下降。為了提高SF的精度,只能通過改變晶體管尺寸和偏置電流,但這又與電路的功耗和速度相矛盾。此外,SF的另一個缺點是增益和線性度對設計參數不敏感,但這同時也是其優點,其對電路失配也不敏感。

相比于SF而言,單位增益放大器本身的增益也并非單位增益,需要通過設計參數調整得到。比較常用的是源級弱化交叉耦合對結構,其設計裕度比普通的差分對結構和SF結構都更大。根據本設計對帶寬的要求,負載電阻不能太大。故為了保證增益,偏置電流和管子尺寸都比較大,影響電路的功耗;同時為了提高偏置電流管的電壓裕度和輸入共模范圍,又要引入大的源級衰減電阻,而此電阻又會引入噪聲跟諧波,影響電路的動態精度。

通過對以上兩種結構的分析比較,結合本設計對速度和功耗的指標要求,本文采用加強型源隨器技術,設計了一種可滿足本設計要求的高增益、高帶寬的緩沖器。

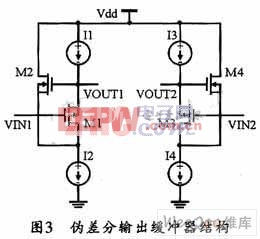

圖3是本設計所采用的緩沖器結構。其中P管源隨器為主管,在此源隨器的基礎上加入的N管用來鉗位P管的源漏電壓,以使得漏源電壓為常數。在深亞微米工藝中,MOS管的最小溝道長度會減小,輸出電阻變小且受短溝效應和背柵效應影響而是非線性,從而導致電路增益降低并引入了失真。N管可使主管的漏源電壓恒定,從而使得短溝效應降低,也降低了P管的漏源電壓,提高了輸出電阻,從而改善了增益和線性度。與傳統的級串型源隨器相比,由于漏端跟柵端電壓幾乎保持相同的電壓相位和幅度,柵漏電容也降低了,故輸入電容不但不會增加,反而降低了。而低的輸入電容又避免了對高頻輸入信號的衰減。

評論