低壓CM0S帶隙基準電壓源設計

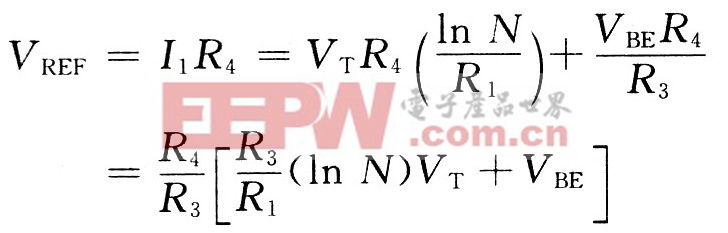

輸出電壓VREF為:

電路中的溫度補償系數K為:

通過調節R4的值,可以調節輸出電壓VREF的大小。在電源電壓變化時,P2,P3,P4的漏源電壓值保持不變,與電源電壓無關,其柵極電壓由運放調節。為了降低電路的復雜度,應用電流反饋原理,運放采用簡單的一階運放,由于VDD的變化多于GND的變化,故運放的輸入采用NMOS的差分對結構。因為整個電路在低壓下工作,故整個電路設計的重點是要保證低壓下運放的正常工作。

由于帶隙基準源存在兩個電路平衡點,即零點和正常工作點。當基準源工作在零點時,節點1、2的電壓等于零,基準源沒有電流產生。固需要設計一個啟動電路,避免基準源工作在平衡零點。本設計的啟動電路由N5、N6和P7構成。當電路工作在零點時,N6管導通,迅速提高節點1、2的電壓,產生基準電流,節點1的電壓通過P7和N5組成的反相器,使N6管完全截止,節點1、2的電壓回落在穩定的工作點上,基準源開始正常工作。

電路的器件參數如表1所示,P2,P3,P4管的尺寸較大,是為了降低電路中的1/f噪聲。電流鏡的負載管P5,P6和差分對管N1,N2的寬長比較大,以抑制電路的熱噪聲。由于電路中的電阻值較大,故在工藝中用阱電阻實現。電容C0有助于電路的穩定,同時還可以減小于運放的寬度,有助于降低噪聲的影響。本文引用地址:http://www.104case.com/article/180881.htm

2 仿真與結果分析

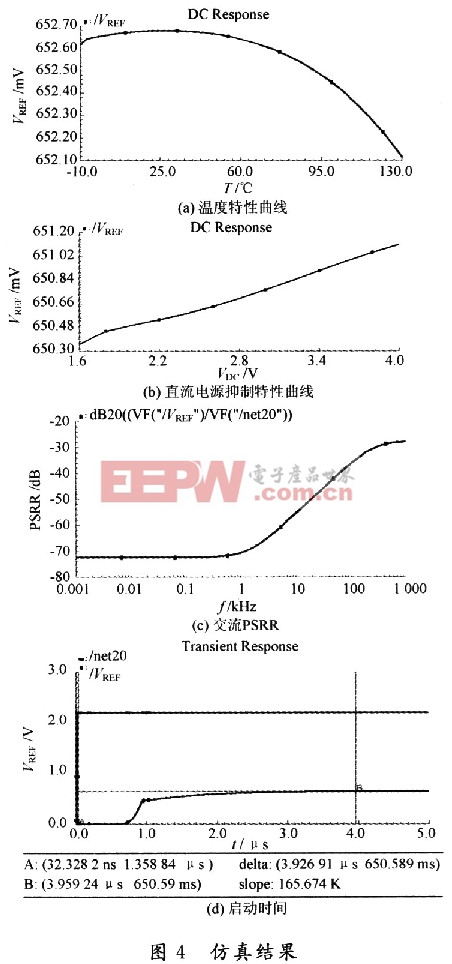

在Cadence設計平臺下的Spectre仿真器中基于CSMC 0.5 μm CMOS工藝模型對電路進行了仿真。得到電路的溫度特性曲線、直流電源抑制特性曲線、交流PSRR特性曲線、啟動時間曲線如圖4所示。各項仿真結果參數如表2所示。

3 結語

在應用典型CMOS電壓基準源的基礎上,綜合一級溫度補償、電流補償技術,設計了帶隙電壓基準源電路。該帶隙基準源電路的電源工作范圍為1.6~4 V,工作溫度為-10~+130℃,基準輸出電壓VREF為(650.5±0.5)mV,溫度系數可低至2.0 ppm/℃,電源抑制比為-70 dB。仿真結果證明了設計的正確性。

評論