基于JK觸發(fā)器的12歸1計(jì)數(shù)器的設(shè)計(jì)與實(shí)現(xiàn)

摘要:觸發(fā)器是數(shù)字電路的基本邏輯單元之一,也是構(gòu)成各種時(shí)序電路的最基本邏輯單元。文中給出了基于JK觸發(fā)器來設(shè)計(jì)十二歸一計(jì)數(shù)器的設(shè)計(jì)和實(shí)現(xiàn)方法,并通過EWB軟件進(jìn)行了仿真。

關(guān)鍵詞:JK觸發(fā)器;12歸1;計(jì)數(shù)器;時(shí)序電路

O 引言

在現(xiàn)實(shí)生活中,任意進(jìn)制的歸一應(yīng)用都十分廣泛。觸發(fā)器是數(shù)字電路中的基本邏輯器件,本文給出了用JK觸發(fā)器設(shè)計(jì)實(shí)現(xiàn)十二歸一計(jì)數(shù)器的設(shè)計(jì)方法,該方法也可以擴(kuò)展到設(shè)計(jì)實(shí)現(xiàn)任意進(jìn)制的計(jì)數(shù)器。

1 計(jì)數(shù)器的基本原理

根據(jù)12歸l計(jì)數(shù)器的設(shè)計(jì)要求,可利用4個(gè)JK觸發(fā)器來實(shí)現(xiàn)12歸1計(jì)數(shù)器,其JK觸發(fā)器的功能表如表1所列,計(jì)數(shù)狀態(tài)表如表2所列。

12歸1計(jì)數(shù)器通常有兩種功能,即計(jì)數(shù)和置1,通過分析JK觸發(fā)器的功能表和計(jì)數(shù)器狀態(tài)表,可以看到,要實(shí)現(xiàn)計(jì)數(shù),也有兩種方法,即同步計(jì)數(shù)和異步計(jì)數(shù);而要實(shí)現(xiàn)置1,同樣也有兩種方法,即利用JK觸發(fā)器的端異步置1和直接利用J、K端同步置1。

2 異步計(jì)數(shù)/異步置1法的設(shè)計(jì)

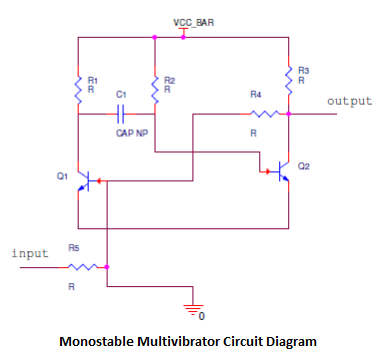

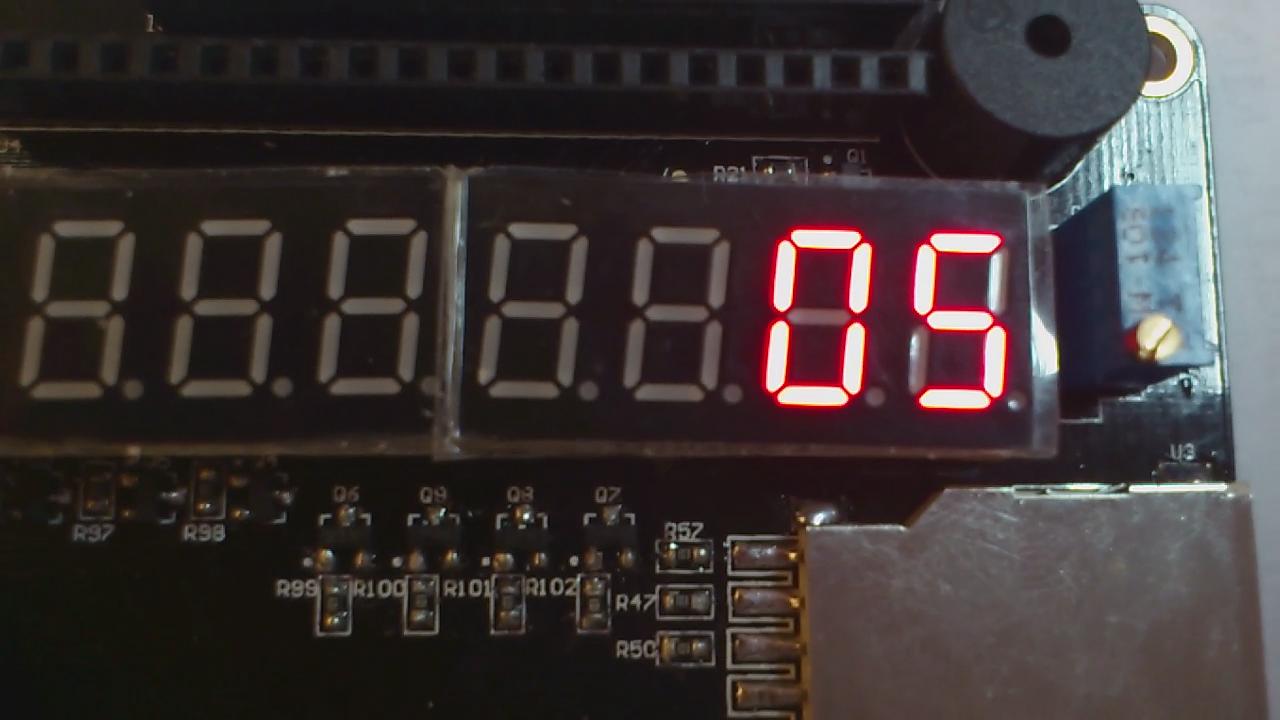

異步時(shí)序電路是指無統(tǒng)一CP,輸入時(shí)鐘脈沖只作用于最低位觸發(fā)器,各觸發(fā)器間串行連接,即狀態(tài)更新逐級進(jìn)行的一種計(jì)數(shù)器電路。圖1所示就是一種異步計(jì)數(shù)器的電路圖。

3 同步計(jì)數(shù)/異步置1法的設(shè)計(jì)

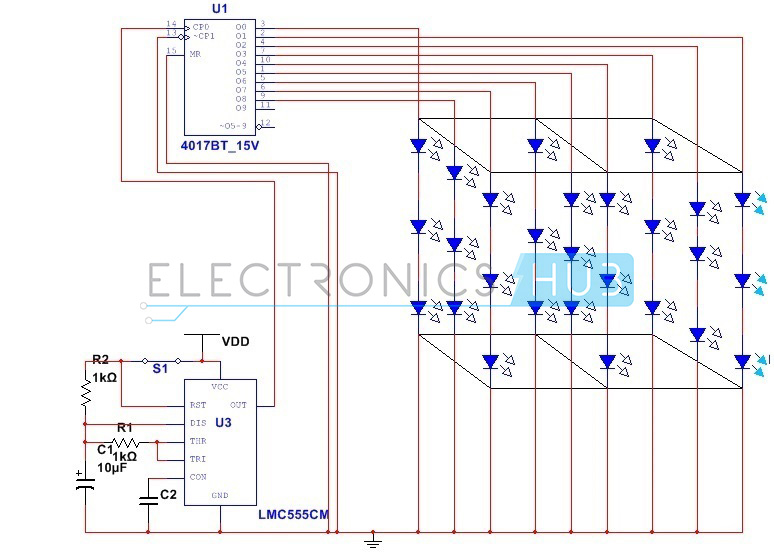

所謂同步時(shí)序計(jì)數(shù)器,是指有統(tǒng)一的CP、狀態(tài)更新與CP同步、而且共用的信號源。分析12歸1的狀態(tài)表,可以看出:當(dāng)?shù)臀蝗孔優(yōu)?時(shí),高位進(jìn)位。而將JK觸發(fā)器的、端置1,即為異步置l,其所設(shè)計(jì)的同步計(jì)數(shù)器電路如圖2所示。

評論