中頻解調電路中的I2C總線接口電路

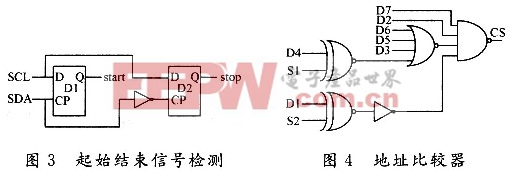

(2)地址檢測。根據設計要求,I2C總線每次通信輸入8位地址數據和控制數據,電路進行地址比較以后,如果地址正確,則接收控制數據。為了防止地址沖突,增加了地址選擇位,具體實現如圖4所示。D7~D1為發送的數據地址,由于S1,S2是可設置端口,有4種組合,即總線接口有4個地址,分別為1000010,100001l,1001010,100101l,只有當D7~D1為100S101S2時,選址成功,即可以有效解決地址沖突。

(3)數據串并與并串的轉換。電路中,串行數據轉換為并行數據、并行數據轉換為串行數據主要由移位寄存器完成。它以并行方式與輸出模式寄存器和讀狀態寄存器相連;以串行方式與數據線SDA相連。發送的數據由讀狀態寄存器裝載到數據寄存器中。發送后數據又從串行通道返回數據寄存器中,接收數據時,數據寄存器裝入SDA線上的數據。

(4)內部總線狀態的檢測。讀狀態寄存器連接著內部總線的8位狀態位S0~S7,在讀狀態時,該寄存器將內部總線的狀態讀進去,再以并行方式傳給移位寄存器,移位寄存器以串行的方式傳給數據線,即內部總線狀態被主控器讀取,如圖5所示。

(5)并行端口的擴展。根據芯片功能的需要,設置了4組輸出模式寄存器,分別為調整模式寄存器、備用寄存器、開關模式寄存器、數據模式寄存器。寄存器個數可根據芯片功能的需要進行并行擴展,由于每一組寄存器都對應著相應的子地址,所以每一組寄存器對應相應的時鐘CPl,CP2,CP3,CP4和控制端C1,C2,C3,C4。這些時鐘和控制端由1個帶控制端的2/4譯碼器輸出,所以每次只有1組寄存器工作,如圖5

所示。

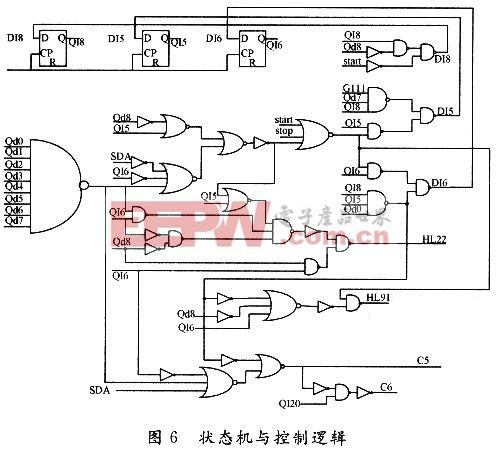

(6)狀態機與控制邏輯的設置與優化。狀態機與控制邏輯作為I2C接口的控制中心,主要用于控制I2C接口電路的使能、啟動、終止。圖5給出寄存器組圖的應答、復位、選址及中斷請求等。通過對狀態機與控制邏輯的優化設置,僅使用3位狀態作為狀態機的狀態端,在滿足更多功能的基礎上,電路更易于實現。如圖6所示,3個觸發器的輸出Q18,Q15,Q16為狀態機的狀態,Qd0~Qd8為移位寄存器的輸出,HL91為移位寄存器的可控復位端,G111為地址檢測位,HL22為應答位,C5,C6為移位寄存器與讀狀態寄存器的控制端。

上電后,狀態機的初始值被置位為全0。HL91作為移位寄存器輸入端的置位端將移位寄存器的輸入端置0。當初始信號到來時,start信號變為1,此時狀態機的狀態變為100,開始傳送尋址字節;當8位地址傳送完畢后,假設為寫狀態,此時Qd8變為高電平,應答位HL22由高電平變為低點平,狀態機的狀態變為110。HL91變高將移位寄存器的輸入置0,響應結束后,應答位由低電平變為高電平,狀態機的狀態變為010,此時開始傳輸數據。

I2C總線開始工作后,主控器便發送尋址字節給移位寄存器,在移位寄存器將7位串行地址并行移出,且與地址寄存器的從地址進行比較,當地址相同時,Glll變為1,尋址成功,此時應答信號HL22變為0,并告知主控制器。在尋址成功后,如果為讀狀態,則在傳完該字節之后,產生應答信號,狀態機變為100,移位寄存器控制端C5變為低電平,讀狀態寄存器的控制端C6變為高電平,讀狀態寄存器讀入內部總線狀態。其中,QI20是與讀/寫有關的控制端,響應結束后,狀態機狀態變為110,此時,C5變為高電平,C6變為低電平,讀狀態寄存器將存儲的8位狀態位并行傳給移位寄存器;移位寄存器將狀態串行移出,發送給主控制器;主控制器接收到8位狀態位后,發送非應答信號給接收器,使它釋放數據線;響應結束后,主控制器產生結束信號,結束數據傳送。

如果為寫狀態,在接收器產生應答信號后,主控器將發送子地址給移位寄存器。根據輸出模式寄存器功能的不同,分別對應3組不同的子地址。在狀態機與控制邏輯的作用下,子地址具有自動加1功能,所以在讀寫多字節時,可以實現自動操作,加上后面的2/4譯碼器,每次只選通1路輸出模式寄存器,如圖7所示。

DIY機械鍵盤相關社區:機械鍵盤DIY

隔離器相關文章:隔離器原理

評論