基于PCI總線的塔康視頻信號產生電路設計

3 系統軟件設計

3.1 FPGA功能實現

FPGA開發采用Altera綜合開發平臺Quartus II 6.0,利用VHDL語言開發了雙口RAM、總線控制、地址譯碼、D/A轉換器控制、脈沖序列產生、波道控制和詢問信號檢測等7個功能模塊,分別為:1)設計雙口RAM,用于實現PCI9054數據和DSP數據的交換:2)實現PCI9054本地總線邏輯控制,例如:對雙口RAM的讀寫邏輯;3)實現DSP的地址譯碼邏輯,根據不同的指令選擇不同的功能單元;4)實現D/A轉換器的邏輯控制;5)產生脈沖序列。根據需要,可產生基準脈沖、填充脈沖、應答脈沖、隨機脈沖,組成脈沖序列;6)實現波道控制和衰減控制;7)實現對詢問信號的檢測等。FPGA內部邏輯如圖5所示。本文引用地址:http://www.104case.com/article/180513.htm

3.2 DSP程序設計

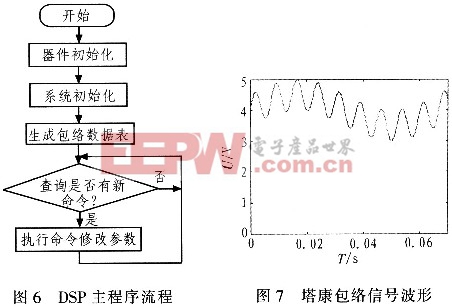

DSP片上程序以CCS2.0為開發平臺,主要包括器件初始化程序、系統初始化程序、包絡數據(由15 Hz和135 Hz正弦信號組成)產生程序、INTO中斷程序、INTl中斷程序和定時器中斷程序。其中,器件初始化程序完成片內外設的初始化(如鎖相環時鐘發生器參數的設置,定時器參數的設置,可屏蔽中斷的設置等);系統初始化程序完成整個系統的初始化(I0地址分配、全局變量的初始化設置和系統外設的初始化);包絡數據產生程序主要產生15 Hz正弦數據表和135Hz正弦數據表兩張函數表;INT0中斷程序完成接收PC指令:INTl中斷主要接收到詢問信號后完成應答功能;定時器中斷程序完成查找函數表并通過計算產生包絡數據,啟動D/A轉換電路產生包絡信號,同時產生脈沖選擇信號,控制FPGA輸出脈沖序列。DSP主程序流程如圖6所示。塔康包絡信號波形如圖7所示。

3.3 PCI驅動程序開發

根據Windows提供的驅動程序模型,使用VC++6.0和DriverStudio軟件編寫了WDM驅動程序。該驅動程序對PCI9054起到內存映射和中斷管理的作用。驅動程序安裝后,應用程序對PCI卡的訪問可通過調用WindowsAPI的函數CreateFile()實現。這樣,對端口的操作最終表現為對一個文件的操作。

4 結論

針對系統模塊化的設計要求,開發了基于PCI9054的塔康視頻信號產生板卡。基于PCI總線的塔康視頻信號產生電路適用于多種工控機平臺,通用性強,并且滿足設計要求,實際使用效果良好,因此具有良好的應用前景。

評論