新型BiCMOS帶隙基準電路的設計

圖2中各個MOS管具有相同的長寬比。晶體管Q1與Q2發射極面積相同、Q3與Q4發射極面積相同、Q1與Q3的發射極面積比為1:n。Rs和Rt為修調電阻。放大器AMP1和AMP2處于深度負反饋。AMP1使得a和b兩點的電壓相等,而AMP2使得電壓VR2等于Vbe3。通過M1、Q1、Q2支路和M2、Q3、Q4支路的電流相等設為I1。通過M6、R2支路的電流設為I2。可得到如下的表達式:

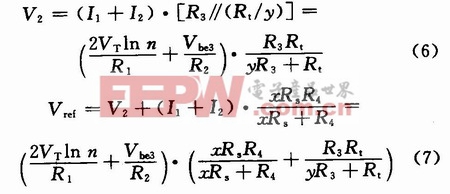

式中:I1具有正的溫度系數,I2具有負的溫度系數。I2和I2分別鏡像到M3和M7求和后得到不隨溫度變化的基準電流。此電流通過R3,R4以及修調電阻Rs,Rt產生基準電壓Vref。由于IC工藝的隨機性,薄膜電阻會有(10%的變化,所以本設計用外部修調電路對輸出基準電壓進行精確控制,通過激光修調或數字電路控制修調電阻的個數可以對輸出電壓進行微調。作為一般結論考慮串聯電阻Rs個數為x,并聯電阻Rt的個數為y,得到:

通過式(6)可知,調節R2/R1的值,使Vref的溫度系數近似為零。通過增大串聯電阻Rs個數x來增大Vref,而增加并聯電阻Rt的個數y達到減小Vref的目的。

AMP1的反向輸入端串聯2個(而不是一個)正向二極管接地起到了減少噪聲的作用,亦可以抑制放大器的失調電壓對Vref的影響。為了進一步減小運放失調對參考電壓的影響,可以考慮較大的Q1、Q3發射結面積比值。此外,由于引入了修調電路,輸出電壓Vref可以穩定在0.5 V。

1.3 次級電壓的生成

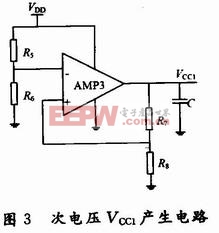

為了改善電源抑制比,不直接用主電源來供電,而是使用主電源電壓Vcc來產生一個次電壓Vcc1來供電(如圖2所示),以提高這種新型帶隙基準電路的電源抑制比。其電路如圖3所示。

該電路中,AMP3處于深度負反饋狀態,根據運放虛短原理可知

電容C的作用是去除電源電壓交流成分的影響。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論