AD9822及其在面陣CCD系統中的應用

2 AD9822的結構及其工作原理

2.1 AD9822簡介

AD9822是美國ADI公司的一款面向CCD的完善的低功耗單通道模擬信號處理器,內含最高15 MSPS的相關雙采樣(CDS)電路、可編程增益放大器(PGA)、14位精度的最高采樣率為15 MSPS的A/D轉換器,可以對面陣CCD信號和模擬視頻信號進行A/D轉換。AD9822以其高精度、高速度的模數轉換能力,廣泛應用在工業控制、醫療儀器、科學研究等領域的高精度圖像采集系統中。

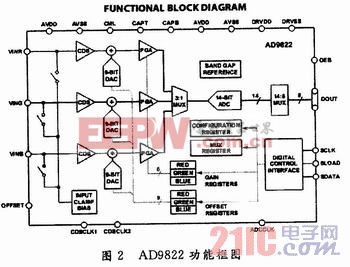

圖2為AD9822的內部結構,它提供三通道的信號輸入,每個通道由輸入箝位、相關雙采樣、DAC補償以及可編程增益放大器PGA和高精度A/D轉換器構成。CCD輸出信號先后在相關雙采樣處理單元、增益控制處理單元以及A/D轉換處理單元作用下,轉換成數字信號輸出。

2.2 AD9822的工作原理

本設計采用的是單路CDS模式,CCD視頻信號在進入AD9822之前,首先要進行交流耦合。由于CCD的輸出信號包含了一個較大的直流成分,這個直流量會超出后接信號處理芯片允許的輸入信號電壓范圍,因此,需要從信號中去除這個大的直流分量。在實際電路中,將CCD的輸出信號經過一個 O.1μF的耦合電容連接到AD9822的CCD信號輸入引腳。在本設計中,由于CCD輸出信號的幅值為1.9 V,而AD9822允許的輸入信號幅值為2 V,所以,經過交流耦合后,CCD輸出信號可直接進入AD9822。之后,視頻信號首先經過的是輸入箝位電路,箝位電路用來消除信號鏈中的殘留偏壓,并且跟蹤CCD暗像素的頻率成份,錯誤的信號將被過濾掉,所以噪聲降低,去掉偏壓還可減小對增益改變的影響。

經過箝位后的信號進入相關雙采樣電路。電路對每個CCD像素信號進行兩次采樣,以提取視頻信息和抑制低頻噪聲。由于CCD每個像素的輸出信號中既包含有光敏信號,也包含有復位脈沖電壓信號,若在光電信號的積分開始時和積分結束時,分別對輸出信號采樣,并且使得兩次采樣的間隔時間遠小于時間常數 RonC(Ron為復位管的導通電阻),則這樣2次采樣的噪聲電壓相差無幾,而這兩次采樣的時間又是相關的。若將兩次采樣值相減,就基本消除了復位噪聲的干擾,得到信號電平的實際有效幅值。如圖1所示,CDSCLK1和CDSCLK2分別用來對參考電平和數據電平進行采樣,ADCCLK為ADC的采樣時鐘。它們和CCD視頻信號的位置關系決定了信號質量的好壞。CDSCLK1,CDSCLK2和ADCCLK均由FPGA實現。

經過相關雙采樣后,信號被送入增益放大器PGA。這里先經過一個DAC補償的反饋網絡,以便更穩定地調節圖像信號。DAC offset可以提供-350~+350 mV的信號補償,步進階數為512,即9 b的分辨率。具體數值通過補償寄存器進行配置。增益放大器PGA的增益范圍為1~5.7 dB,步進階數為64階,分辨率為6 b,通過PGA增益寄存器進行配置。PGA的增益值和PGA Gain寄存器中的值之間的關系如下:

式中:G為增益寄存器中的十進制的值,變化范圍為0~63。

合理地設置增益放大器,可將信號調節至ADC允許的最大量程,有利于提高ADC的動態范圍,從而提高圖像質量。

經過以上信號預處理后,信號進入A/D轉換器,AD9822使用的是高性能14 b模數轉換器,高速低耗。差分非線性性能在O.7LsB左右。由CCD視頻信號的數據輸出速率可知,AD采樣率為10 MHz。因為AD9822只有8個數據輸出引腳,因此采用分時輸出高8位和低6位的方法來實現14位數據的輸出。采樣時鐘ADCCLK和輸出數據關系如圖2所示。輸出數據送入低壓差分線驅動器DS90C031后轉換為差分信號,而后送到下一級處理器進行處理。

2.3 AD9822內部寄存器的配置

由上面的介紹可知,AD9822的各種功能模式由其內部寄存器控制,通過三線串行接口SLOAD,SDATA,SCK對內部寄存器寫數據就可實現對其功能模式的配置。AD9822共有8個8 b的內部寄存器,各寄存器的每一位控制不同的內容。其中,配置寄存器控制芯片的工作模式和偏置電壓。MUX寄存器控制采樣通道的順序。PGA寄存器和補償寄存器各有3個,分別對紅、綠、藍3個通道做增益控制和信號補償。設計中,由FP-GA提供三線串行接口的時序及數據。

3.AD9822初始化及工作時序的實現

3.1 現場可編程門陣列(FPGA)

隨著電子技術的不斷發展,電子系統的設計方法也發生了很大的變化,基于EDA技術的芯片設計已經代替了傳統的設計方法成為電子系統設計的主流。現場可編程門陣列(FPGA)是應用極為廣泛的一類可編程專用集成電路(ASIC),工程師可以利用它在實驗室里設計出所需的專用集成電路,從而縮短產品的開發周期,降低開發成本。此外,FPGA還具有可重復編程和在系統重構的特性,使得硬件的功能可以像軟件一樣通過編程來修改,這樣就極大地提高了電子系統設計的靈活性和通用性。本文選用Xilinx公司的FPGA芯片XC3S50器件,結合ISE10.1開發工具,可以實現電路設計、仿真、器件編程等全部功能,開發調試靈活。

3.2 AD9822初始化設置和工作時序的實現

要使AD9822正常工作,需要為其提供初始化設置和驅動時序,初始化設置用于設定該芯片的工作狀態,驅動時序為A/D轉換提供正確的采樣時鐘。選用硬件編程語言VHDL設計AD9822的初始化設置和驅動時序。VHDL采用自頂向下的設計方式,具有很強的系統硬件描述能力和系統仿真能力。

評論