基于MPEG-2算法的列車語音記錄設備

前言

列車運行監控記錄裝置在鐵路的安全運輸過程中發揮了巨大的作用,但不足的是沒有語音記錄功能。為了解決這個問題,按照鐵道部的技術要求,本文研究開發了一種新型列車語音記錄設備。該設備主要用于對乘務員機車聯控進行錄音,并可協同監控裝置分析行車事故,為機務部門和運輸部門的科學管理提供新的技術手段。鑒于常見設備的技術指標及標準,對于語音的數字化,以16KHz的采樣頻率、16位量化精度進行采樣,在編碼方面,采用MPEG-2壓縮編碼方式。

硬件系統組成

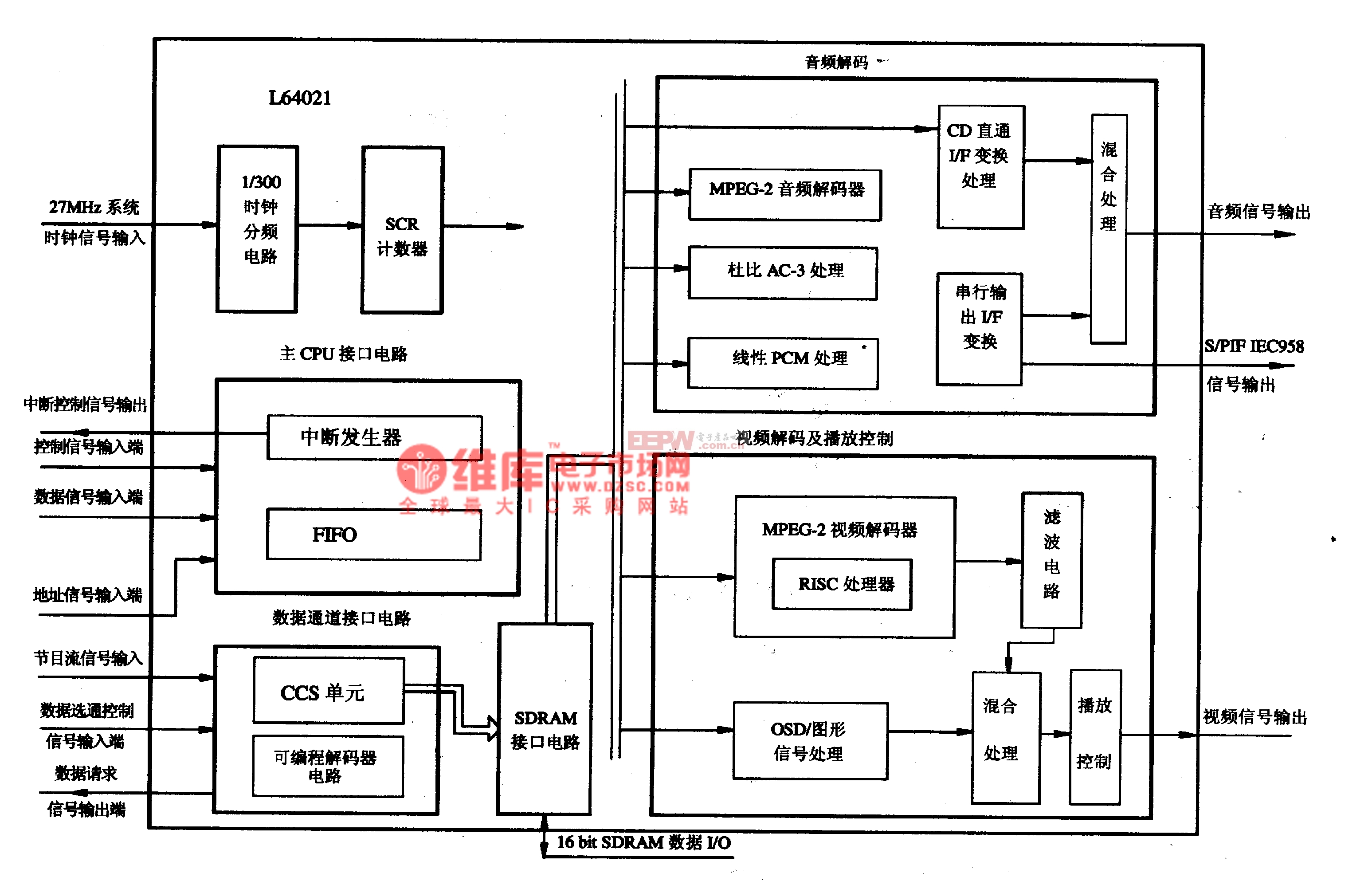

該語音記錄設備如圖1所示,整個系統由 ADC、DSP、CPLD控制器、Flash大容量存儲器及LCD顯示屏等組成。

在本系統中,ADC用來完成信號的轉換,數據格式在16、18、20位之間可選,DSP為系統的核心數字處理器,功能強大,完成數字信號的壓縮編碼,CPLD用于數據傳送的控制以及對ADC、Flash和LCD顯示屏等器件的初始化檢測設置, Flash用來存儲數據, LCD顯示屏用來顯示當前系統的狀態,如運行等待和數據處理等。系統上電后,若有語音信號,則輸入ADC,得到一串數字信號送入DSP 進行數據壓縮編碼,經過壓縮編碼的數據由CPLD存儲到Flash中,整個系統以流水線的方式工作,數據的采集、壓縮編碼和存儲同時進行。

A/D轉換器UDA1341TS

UDA1341TS是由Philips公司生產的一款單片立體聲A/D、D/A轉換器,工作電壓為3.0V,信噪比為97dB,具有雙通道輸入功能,采樣頻率在16,32和44.1KHz之間可選。

UDA1341TS與DSP構成語音信號采集系統,主要涉及到位采樣時鐘(BCK)、字同步時鐘(WS)、采樣數據輸出(DATAO)、系統時鐘輸入(SYSCLK)這幾個對時序有要求的引腳。系統中,DATAO作為輸出引腳,與DSP的BDR0引腳相連;BCK、WS、SYSCLK作為輸入引腳,其時序由DSP供給。UDA1341TS的系統時鐘只能是256Fs、384Fs、512Fs,通過對狀態寄存器的SC0位和SC1位編程可實現系統時鐘的選擇設置。這里Fs是語音信號的采樣頻率。在采樣數據時,WS用來指明UDA1341TS的DATAO輸出的有效數據。當系統對VINL(左聲道)端口進行采樣時,WS的上升沿表明一幀數據的起始,下降沿表明一幀數據的結束;當系統對VINR(右聲道)端口進行采樣時,WS的下降沿表明一幀數據的起始,上升沿表明一幀數據的結束。

圖1 系統總體結構圖

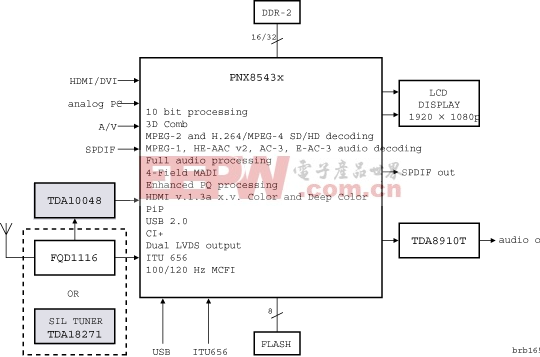

UDA1341TS提供了一個L3端口,利用CPLD控制器對L3的L3DATA、L3MODE和L3CLOCK三個引腳進行編程,可以設置其內部的寄存器。當L3MODE引腳為低電平時,通過L3DATA引腳輸入寄存器地址信息;當L3MODE引腳為高電平時,通過L3DATA引腳輸入有關寄存器設置的數據信息(如設置芯片系統時鐘頻率、數據輸入格式、芯片工作模式等)。UDA1341TS與DSP的McBSP(多通道緩沖同步串口)相連,各種同步信號由DSP產生,這樣就保證了新數據的正常接收以及已接收數據的正常處理。UDA1341TS與DSP的硬件連接如圖2所示。

語音編碼器TMS320VC5402

數字語音信號的壓縮需要大量的數字信號處理,一般單片機是無法完成的,所以本系統選用TI公司的DSP芯片TMS320VC5402(以下簡稱C5402)對語音信號進行壓縮處理。

C5402通過它的McBSP與語音采樣轉換器UDA1341TS通信。McBSP提供了全雙工的通信機制,以及雙緩存的發送寄存器和三緩存的接收寄存器,允許連續的數據流傳輸,數據寬度在8、12、16、20、24、32位之間可選; McBSP與ADC的通信通過BDR0引腳實現,通信過程的控制則由BCLKR0、BCLKR1、BFSR0等三條引腳實現。

圖2 UDA1341TS與DSP的硬件連接圖

CPLD低速控制

DSP作為高速的運算處理器不適合低速的控制應用。對UDA1341TS檢測、初始化,對LCD的控制以及對Flash的存儲控制都是低速的控制。本系統選用CPLD來完成這些工作, CPLD為Altera公司的EPM7128S,開發仿真環境為Altera公司的MAX-PLUSII。因為DSP的地址線A0、A1、A2要被某些芯片使用,所以選取A3-A7、A15共6根地址線和I/O空間選擇信號共同產生系統中各芯片的選通信號。CPLD中的控制電路負責產生各種讀寫信號,如Flash的讀信號MEM_RD和寫信號MEM_WR等。

在該系統中,C5402要產生許多控制信號(如Flash程序頁的選擇信號PPG2-PPGO等),同時也要監視和讀取外部的狀態。因為C5402只有兩個通用I/O引腳,所以用CPLD來對其進行I/O端口擴展。CPLD內部通過一個8位DFF觸發器實現對數據的輸出。另外,通過8個三態門,將8位輸入狀態放到C5402數據總線的低8位上。C5402有4個中斷輸入。CPLD的中斷選擇模塊可以從最多8個外部中斷信號中選擇4個作為C5402的中斷輸入,提高了系統的靈活性。

圖3 系統主程序

軟件設計

軟件設計主要包括ADC的程序設計,語音數據的壓縮編碼等。

ADC的程序設計

ADC以16KHz的采樣頻率、16位量化精度進行采樣,采樣的位同步信號、幀同步信號、數據位時鐘信號均由DSP提供,所以對McBSP相關寄存器的編程,如引腳控制寄存器(PCR)的編程,串口控制器(SPCR1,SPCR2)的編程,接收控制寄存器(RCR1x,RCR2x)以及發送控制寄存器(XCR1,XCR2)的編程會影響語音信號的最終效果,所以用戶在開發之前必須詳細參閱相關資料。

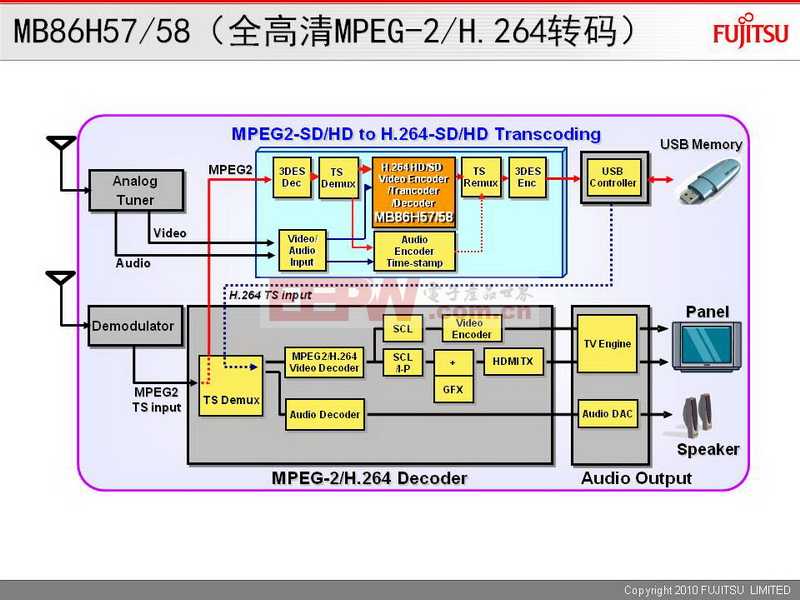

圖4 幀內編碼流程

本文采用通用的MPEG-2語音壓縮編碼算法,該算法是幀數據結構編碼,一幀的樣點值是576,以UDA1341TS 的16KHz采樣頻率計算,一幀數據的編碼要求在72ms內完成。C5402的指令周期是10ns,在滿足算法要求的情況下,進行雙通道實時編碼約需要10ms,所以C5402可以完成該算法的實時編碼。主要包括以下幾方面:濾波器組的運算;心理聲學模型的運算; 量化編碼;幀數據格式化。

濾波器組的作用是完成信號從時域到頻域的映射。心理聲學模型的計算是利用1024點的FFT,對輸入的語音信號進行頻譜分析,再結合時頻映射的結果,計算出各子帶人耳的掩蔽特性。量化編碼是通過各子帶人耳的掩蔽特性和輸出比特率的要求,計算出各子帶編碼所需的比特分配信息,并且對各子帶數據進行線性量化編碼的過程。程序的后續工作是按照MPEG-2標準對數據進行格式化,其目的是使數據編碼后能被正確地解碼,系統主程序如圖3所示。

幀內編碼是DSP按照MPEG-2標準對ADC傳來的數字語音信號進行壓縮編碼,其流程如圖4所示。

結語

系統上電運行后,經多次實驗測試,運行情況穩定。目前該設備已經進行現場調試運用,開始部分裝車運行,滿足了列車語音記錄的實際要求。

參考文獻:

1 Philips Semiconductors. UDA1341TS Product specification [Z].Netherlands:Philips Semicon ductors,2002

評論