一種低功耗系統(tǒng)芯片的實(shí)現(xiàn)流程

3 低功耗設(shè)計(jì)流程

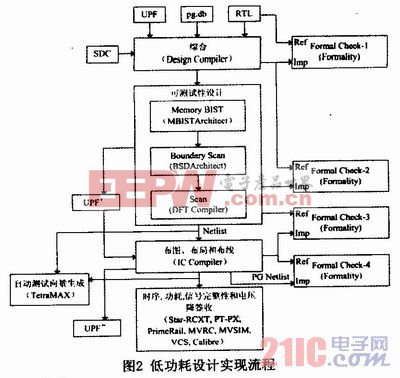

如圖1所示,每個(gè)關(guān)斷電壓域的輸出要插入隔離器件,以防止該電壓域電源關(guān)斷后輸出的不定態(tài)影響別的電壓域正常工作,由于PD6的工作電壓是1.2V,其余的是1.8V,因此要在PD6的輸入和輸出插入電平轉(zhuǎn)換器件。這些低功耗的設(shè)計(jì)意圖寫入U(xiǎn)PF文件,EDA工具根據(jù)UPF實(shí)現(xiàn)設(shè)計(jì)者的想法。整個(gè)設(shè)計(jì)實(shí)現(xiàn)過程中包括RTL代碼的綜合、可測試性設(shè)計(jì)、布局布線、物理驗(yàn)證和網(wǎng)表的等價(jià)形式驗(yàn)證,如圖2所示。

3.1 綜合

RTL代碼的綜合使用Design Compiler(DC),輸入文件為UPF、帶電源信息的庫文件(pg.db)、RTL代碼和時(shí)序約束文件(SDC。在綜合優(yōu)化的過程中,工具會(huì)根據(jù)UPF自動(dòng)地在相應(yīng)的位置插入電平轉(zhuǎn)換器件和隔離器件,優(yōu)化完成后,可以用check_mv_desing命令進(jìn)行正確性檢查。 DC輸出的網(wǎng)表與RTL代碼使用Formality進(jìn)行等價(jià)形式驗(yàn)證。

3.2 可測試性設(shè)計(jì)

在通過等價(jià)形式驗(yàn)證的綜合網(wǎng)表中做可測性設(shè)計(jì)。首先利用MBISTArchitect做靜態(tài)隨機(jī)存儲(chǔ)器(SRAM)的內(nèi)在自測試(MBIST)。輸入文件包括網(wǎng)表、SRAM的模型,輸出帶自測試電路的網(wǎng)表。其次利用BSDArchitect完成邊界掃描測試,輸入文件包括網(wǎng)表和輸入/輸出接口電路的

模型,輸出包含邊界掃描電路的網(wǎng)表。最后利用DFTCompiler完成邏輯掃描測試,輸入文件為UPF、時(shí)序約束文件和網(wǎng)表,利用insert dft命令完成掃描鏈的連接。由于做內(nèi)在自測試和邊界掃描測試電路時(shí)沒有用到UPF,因此在掃描鏈插入后要用check mv desing命令進(jìn)行檢查,電

平轉(zhuǎn)換器件和隔離器件如果缺少用insert_mv_cell插入,如果多余用remove_mv_cell命令刪除。DFT Compiler輸出為網(wǎng)表、新的UPF'、SPF、DEF和時(shí)序約束文件。做完可測試性設(shè)計(jì)的網(wǎng)表和綜合的網(wǎng)表進(jìn)行等價(jià)形式驗(yàn)證。

3.3 布局布線

利用IC Compiler進(jìn)行布局布線,輸入文件有UPF'、時(shí)序約束文件、網(wǎng)表,輸出文件為網(wǎng)表和時(shí)序約束文件。輸出網(wǎng)表要完成等價(jià)形式驗(yàn)證。完成布局布線后的網(wǎng)表使用MVRIC進(jìn)行低功耗設(shè)計(jì)的檢查,用Star-RCXT抽取寄生參數(shù),用PrimeTime進(jìn)行時(shí)序和功耗的簽收,最后用

MVSIM和VCS完成后仿真。最后使用Calibre完成物理驗(yàn)證,輸出GDSII文件。最終的芯片版圖如圖3所示。

3.4 自動(dòng)測試向量的生成

完成布局布線后的網(wǎng)表和DFT Compiler輸出的SPF文件送入TetraMAX中進(jìn)行自動(dòng)測試向量的生成。本文的設(shè)計(jì)生成2576個(gè)向量,故障覆蓋率為98%,并用VCS完成了測試向量的后仿真。

4 結(jié)論

本文闡述了一種低功耗系統(tǒng)芯片的實(shí)現(xiàn)流程。利用該流程實(shí)現(xiàn)了一個(gè)包含4萬寄存器、20萬等效邏輯門的系統(tǒng)芯片,并流片驗(yàn)證,結(jié)果達(dá)到預(yù)期目標(biāo)。

評(píng)論