遙測(cè)艙信號(hào)源的設(shè)計(jì)與實(shí)現(xiàn)

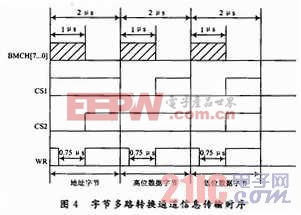

并行數(shù)據(jù)采用8位并行傳輸,每個(gè)信息字的三個(gè)字節(jié)分三次沿8位總線分時(shí)發(fā)送。伴隨信號(hào)CS1,CS2的不同組合構(gòu)成地址字節(jié)、高位數(shù)據(jù)字節(jié)和低位數(shù)據(jù)字節(jié)的區(qū)分標(biāo)志,信號(hào)WR表明信息的發(fā)送。地址按00~7F循環(huán)發(fā)送,數(shù)據(jù)按0000~9FFF循環(huán)發(fā)送,8位總線信號(hào)、伴隨信號(hào)和寫(xiě)信號(hào)傳輸均由245作驅(qū)動(dòng),由這些信號(hào)的信號(hào)線電壓的變化形式表示的信息傳輸時(shí)序如圖4所示。本文引用地址:http://www.104case.com/article/179283.htm

從圖4可以看出,一個(gè)信息字節(jié)的傳輸時(shí)間是2μs,一個(gè)信息字的傳輸時(shí)間是6μs。相鄰兩個(gè)信息字之間的間隔時(shí)間是10μs。

并行數(shù)據(jù)信息在5 ms周期內(nèi)完成后發(fā)送,每個(gè)周期發(fā)送信息的時(shí)間大約為640μs。

采用VHDL語(yǔ)言編寫(xiě)程序,使FPGA輸出固定時(shí)序的LVTTL電平的3路信號(hào),經(jīng)過(guò)2片總線驅(qū)動(dòng)器后,轉(zhuǎn)為T(mén)TL電平的并行數(shù)據(jù)信號(hào)。

3.3 串行RS 422數(shù)據(jù)

串行RS 422數(shù)據(jù)共有3路。通過(guò)FPGA的VHDL程序產(chǎn)生符合RS 422協(xié)議的LVTTL電平數(shù)據(jù),經(jīng)過(guò)RS 422接口芯片進(jìn)行電平轉(zhuǎn)換。

RS 422接口芯片采用Maxim公司的MAX1484,它是1收1發(fā)驅(qū)動(dòng)器,全雙工。

(1)第一路DF422

波特率為500 Kb/s,每幀2.5 ms,幀長(zhǎng)9個(gè)字節(jié)。

(2)第二路ZW422

波特率為240 Kb/s,每幀1 ms,幀長(zhǎng)12個(gè)字,8 b/字。

數(shù)據(jù)格式是:

1位起始位+8位數(shù)據(jù)+1位停止位+10位空閑位其中:8位數(shù)據(jù)是低位在前,高位在后。

(3)第三路YX422

波特率為200 Kb/s,消息塊更新頻率為400 Hz,每個(gè)消息塊6個(gè)字,每字11位:

1位起始位+8位數(shù)據(jù)+1位奇偶校驗(yàn)位+1位停止位

3.4 模擬信號(hào)

通過(guò)對(duì)48 MHz的外部時(shí)鐘分頻產(chǎn)生固定頻率的脈沖方波,幅度為0~3.3 V,采用高速運(yùn)算放大器產(chǎn)生線性比例放大電路對(duì)幅度進(jìn)行調(diào)節(jié)。

運(yùn)算放大器采用AD公司的AD824,支持單電源供電,是低功耗的場(chǎng)效應(yīng)晶體管輸入操作放大器。

3.5 電路設(shè)計(jì)

在設(shè)計(jì)中采取了多種措施以保證信號(hào)源在各種情況下的正常工作。

(1)采用4層PCB板設(shè)計(jì),避免使用過(guò)多分立器件,減小設(shè)備體積,縮短引線,提高可靠性;

(2)電源和器件電源管腳加濾波電容,減小電源噪聲對(duì)器件和電路板的影響;

(3)印制板合理布局、布線,減小各種信號(hào)間的相互干擾;

(4)差分信號(hào)線d+和d-到接口不超過(guò)30 mm,兩信號(hào)線長(zhǎng)度差控制在2 mm以內(nèi),確保滿足LVDS數(shù)據(jù)傳輸帶寬的要求;

(5)電路設(shè)計(jì)中,采取措施盡量提高系統(tǒng)對(duì)各種干擾的隔離以及突發(fā)大信號(hào)的抑制,保護(hù)系統(tǒng)可靠工作。輸出電路串接保護(hù)電阻,在輸出短路時(shí)確保電路完好。

4 結(jié)論

綜上所述,主要介紹了遙測(cè)艙多路可編程信號(hào)源的設(shè)計(jì)與實(shí)現(xiàn),著重對(duì)設(shè)計(jì)中的幾個(gè)關(guān)鍵技術(shù)做了較為詳細(xì)的研究論證。通過(guò)采用FPGA作為設(shè)計(jì)核心,編寫(xiě)VHDL程序產(chǎn)生主要邏輯功能,附加外圍電平轉(zhuǎn)換芯片實(shí)現(xiàn)各種類(lèi)型信號(hào)輸出。實(shí)踐證明,此信號(hào)源完全能夠模擬遙測(cè)艙測(cè)量到的信號(hào),符合設(shè)計(jì)要求。

評(píng)論