具有帶隙結構的遲滯比較器電路設計

(3)整體電路的門限電壓和遲滯電壓

當VFB從低電平逐漸增加時,Ic2>Ic1,于是C點電壓高于D點電壓,Q10導通,Q9截止。當輸入電壓VFB達到帶隙比較器的翻轉門限時,Ic2=Ic1,此時遲滯比較器發生翻轉,Q10截止,Q9導通,設此時的VFB=VOH,則有:

當VFB從超過VOH電壓逐漸減小時,遲滯比較器的工作點發生變化,只有當遲滯比較器的電壓達到下翻轉門限時,遲滯比較器才翻轉,于是當VFB減小到VFB=VOH時,Q10并不導通,VFB繼續減小,當遲滯比較器的電壓達到下翻轉門限時,遲滯比較器才會發生翻轉,Q10導通,設此時的VFB=VOL,則有:

式中:△U是△V等效到IN端的輸入電壓;△V是遲滯比較器的遲滯電壓。于是整體電路的輸入端FB遲滯電壓為△U。它與Q9導通時流過的電流、R8大小有關。調節R9,R10的大小可以改變Q9導通時流過的電流,也就可以調節這個遲滯電壓。改變R8的大小可以直接調整遲滯電壓。

2 仿真驗證

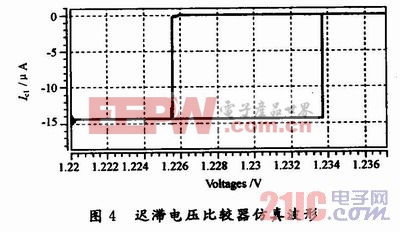

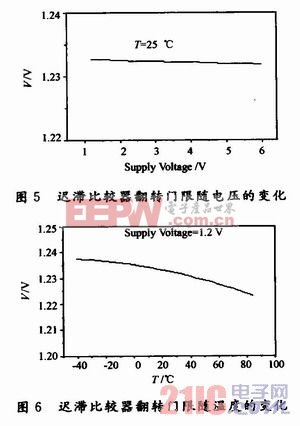

遲滯比較器的仿真波形如圖4~圖6所示,圖4為輸出電流IOUT與輸入信號FB的關系圖。從圖中可以看出,該電路能夠實現8 mV的遲滯功能。圖5和圖6分別為遲滯比較器翻轉門限隨電源電壓和溫度的變化結果。可以看出,遲滯比較器的翻轉門限隨溫度和電壓變化均較小,驗證了電路的穩定性較高。本文引用地址:http://www.104case.com/article/179147.htm

3 結語

傳統的帶隙基準電路和遲滯比較器電路占芯片面積較大,工作電壓和功耗都比較高。本文設計的具有帶隙結構的遲滯比較器工作電壓低至1.2 V,大大節省了芯片面積,適用于微功耗DC—DC轉換器中,主要用于鎳鎘、鎳氫和堿性電池供電的便攜式產品。

評論