一種改進的基于掃描的電路設計

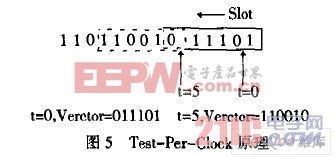

如圖5所示,每個時鐘周期。Slot會往左移動一位,即在Slot內產生一個新的測試向量,而Slot大小可以看成掃描鏈的大小。

不過,由于每個時鐘都要作測試,所以每個時鐘在測試后都會產生新的測試結果。傳統的基于掃描的測試環境里,電路輸出結果傳送出來的同時也將新的測試傳進掃描鏈里。

如果輸出的向量只有一位就不會有這樣的問題。

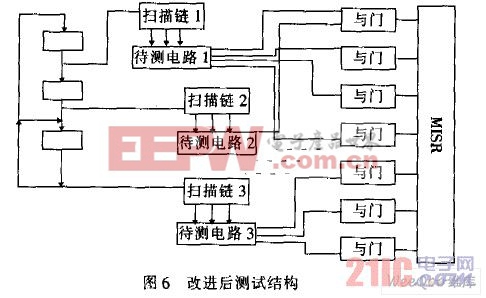

因為我們現在要產生一個新的測試向量所需要的時間只有一個時鐘周期,所以時問剛剛好。但是一般而言,待測電路的輸出向量都會超過一位。所以我們在觀察電路輸出結果這個步驟上就會有問題。為了解決這個問題,需要對傳統的基于掃描的測試電路做些修改。在待測電路的輸出部分,可以用MISR來取代原來的掃描鏈電路,也就是將輸出送到MISR做特征分析,如圖6所示。

但是由于電路越來越復雜,電路的主要輸入與輸出的個數就會很多,如果對這樣的待測電路加測試電路,將會出現外加電路面積過大的問題。所以我們針對MISR的部分提出一個方法,使得因測試而增加得MISR可以盡量地縮小。

縮小MISR的大小最直接的想法是將主要輸出經組合電路壓縮變小,但是這樣會使錯誤覆蓋率降低,使測試向量變多,這些問題在文獻中談到了。造成錯誤覆蓋率降低的原因是如果我們將有共同輸入向量的兩個主要輸出通過組合電路合并的話。將可能會造成原本可以測試到的錯誤,在合并后就測試不到了,所以造成了錯誤覆蓋率的降低。

為了避免這個情況的發生,我們在向量壓縮的過程中。只有將沒有共同輸入向量的主要輸出合并在一起,就不會有問題出現了。如圖6所示,兩個不同的待測電路的主要輸出經過合并以后輸出到MISR,這樣用一個與門代替了一個寄存器以便減少面積,而錯誤覆蓋率則因為兩兩合并的主要輸出端都沒有相同的主要輸出資料,所以就沒有錯誤覆蓋率降低的問題存在,即原來可以被偵測到的錯誤,在經過主要輸出端合并之后仍然可以被偵測到。

4 結論

經過改進后的基于掃描的測試架構,用向量壓縮來減少測試時間,并且將TEST—Per-Scan的測試方式改成了TEST—Per-Clock的測試方式,加快了測試的速度。

評論