變頻器慣性輸出技術

目前所使用的變頻器一般將上述比較過程放在cpu中完成,當cpu遇到干擾復位或程序出錯的時候,變頻器將停止輸出。由fpga來完成三角波和正弦波的比較過程將很好的解決這個問題,利用cpu的強大計算能力實時計算參與比較的正弦波,利用fpga高速度的時鐘精確產生移相三角波,然后在fpga中進行比較輸出。fpga脈沖發生器及慣性輸出原理#e#4 fpga脈沖發生器及慣性輸出原理

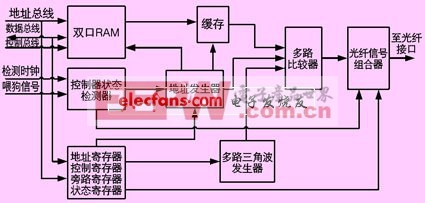

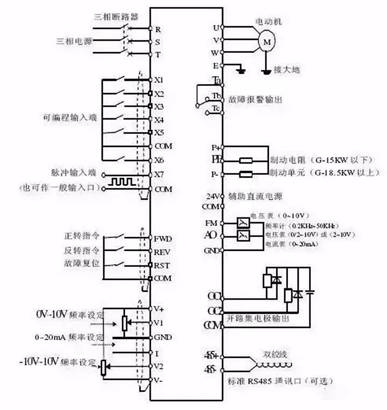

由fpga實現相位移載波spwm調制的結構框圖如圖4所示。fpga與cpu的接口由數據總線、地址總線和控制總線實現,cpu上電后首先對fpga的控制寄存器進行初始化,設置spwm的輸出周期,各路三角波的初始相位和幅值。地址發生器根據周期寄存器的值產生ram讀取地址,輸出數據進入緩存。在每個三角波的谷值處給cpu一個中斷,通知cpu更新數據,在每個三角波的峰值處從ram中讀取數據進入緩存。cpu每次更新數據的同時也更新地址寄存器,指明當前輸出數據的地址長度,此地址長度決定了變頻器輸出的頻率。多路比較器實時將緩存數據與對應三角波進行比較產生spwm波形,光纖信號組合器將每一個功率單元所需信號即左臂信號、右臂信號、閉鎖信號、旁路信號組合編碼成一路串行信號送入光接口。

圖4 fpga實現變頻器慣性輸出結構圖

在fpga內部實現了一個看門狗(控制器狀態檢測器)對cpu進行監視,cpu在正常工作時,在每ms之內必須給fpga一個喂狗信號,當檢測器在2ms沒有檢測到此信號變化則給地址發生器一個信號,地址發生器則根據當前的地址寄存器產生地址從雙口ram中讀取數據,從而實現cpu死機時變頻器輸出的相位和頻率能夠繼續,即具有慣性輸出功能。fpga實現慣性輸出時,狀態寄存器保存當前輸出頻率值和故障標志,以供cpu復位之后讀取。

5 verilog設計與仿真

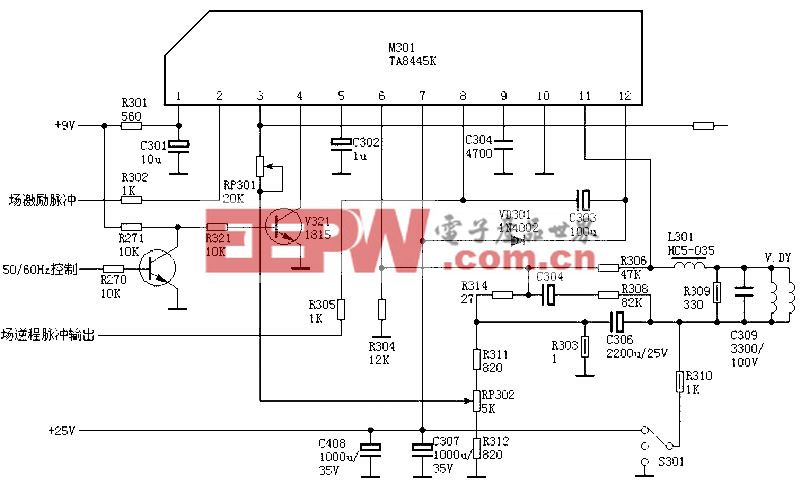

根據圖4的結構框圖應用verilog語言進行設計,選用lattice的xp3系列fpga進行設計,與傳統的基于sram的fpga不同,latticexp3器件不需要外接引導存儲器,因此能提供單芯片的解決方案,從而減少了電路板面積,并簡化了系統制造過程。以控制狀態檢測器為例,當fpga在一段時間內檢測到cpu的喂狗信號沒有改變時,給出cpu異常信號,改變地址控制器的輸出策略。其仿真圖形如圖5所示。

![]()

圖5 cpu狀態檢測器仿真時序圖

評論