用節(jié)能理念設計外部電源方案

近幾年來,電源管理技術有飛躍的發(fā)展,可供選擇的設計方案也越來越多。政府環(huán)保團體及消費者不斷向電子產(chǎn)品廠商施加壓力,敦促他們增加產(chǎn)品功能的同時,也必須降低系統(tǒng)的能耗。目前,便攜式電子產(chǎn)品市場的發(fā)展尤其令人矚目,例如,無線通信產(chǎn)品不斷推陳出新,功能也越趨多樣化,是帶動整個市場發(fā)展的功臣。照目前的發(fā)展趨勢看,移動電話、個人數(shù)字助理、MP3播放機、數(shù)字相機及便攜式電子游戲機都朝著外型更小、速度更高、功能更齊備的方向發(fā)展。為了確保/通話時間/(即電池壽命)可以延長至滿意的水平,工程師便一直致力于改善電源供應子系統(tǒng)的設計。

便攜式電子產(chǎn)品的電池壽命取決丁兩個關鍵要素,其一是電源轉換效奉,而另一個因素是系統(tǒng)的能源管理方法。電源轉換系統(tǒng)負責將電池的供電電壓盡量以最高的效率轉為設計規(guī)定的供電干線電壓,而能源管理系統(tǒng)則針對實際的應用情況,實時提供剛好能滿足其需要的供電,以節(jié)省能源。

3.1提高穩(wěn)壓器效率是有效的節(jié)能辦法之一利用PowcrWis技術降低能耗

新—代的節(jié)能技術側重于調節(jié)處理器的頻率及電壓以降低能耗。

對于以電池供電的系統(tǒng)來說,究竟系統(tǒng)能否長時間處于開啟狀念,取決于其能耗的大小。單單降低其頻率只會減少具平均功耗:但不會減少某一計算上作所需耗用的能源。系統(tǒng)電壓必須調低,才可真正叫節(jié)省能源。動態(tài)電壓調節(jié)(DVS)及自適應電壓調節(jié)(AVS)這兩種電源管理技術都可降低系統(tǒng)電壓。

什么是自適應電壓調整?該技術有哪些優(yōu)點?用于跟蹤系統(tǒng)處理器的性能變化的嵌入式自適應電源控制器(APC)作出自適應電壓調整。APC 通過一個 PowerWise 高速低電源接口將系統(tǒng)處理器的性能(頻率)、溫度和處理變化準確地傳遞給外部適應電源管理芯片。然后,該電源管理單元根據(jù)性能需求自動調整系統(tǒng)處理器的供給電壓.以前的電壓調整方案都是開環(huán)回路。CPU 控制在頻率/電壓檢查表中維護的電壓,通過一個專用接口和電源管理電路來提供電壓。檢查表中的值是否是假與最糟糕的情況底下的值。自適應電壓調整減輕了 CPU 干擾并降低了閉環(huán)回路方式的壓.PowerWise 技術提供的自適應電源管理與 ARM 的 Intelligent Energy Manager 提供的準確動態(tài)性能設置相結合,提供了空前理想的結果。

而動態(tài)電壓調節(jié)(DVS)技術先將不同的電壓及頻率配對成不同的組合,調節(jié)時便根據(jù)實際需要挑選最適用的電壓/頻率組合。己可提供多款電源管理集成電路PMIC,其中包括可支持DVS模式的LP3906、LP3907,以及可支持DVS和AVS兩種模式的LP5550、P5551及LP5552。動態(tài)電壓調節(jié)(DVS)技術可以節(jié)省耗電及能源,還為供電電壓預留一些額外的空間,以支持不同上藝及溫度的系統(tǒng),這個預留的額外中間雖然足以應付最環(huán)的情況,但實際應用時便會浪費較多耗電。我們只要關閉系統(tǒng)的電源供應環(huán)路,控制環(huán)路便可靈活調節(jié)操作電壓,并將之降至最低,以便盡量節(jié)省能源。PowcrWis技術便是利用這個方法節(jié)能。

3.2 PowerWise特征

PowerWise接口(PW)可以支持智能的能源管理系統(tǒng)。

PowerWise是一種針對系統(tǒng)整體需要的能源管理技術,確保以電池供電的電子產(chǎn)品可利用自適應電壓調節(jié)(AVS)技術以及控制不同狀態(tài)的切換。PowerWise技術采用閉環(huán)AVS系統(tǒng)搭配高速的串行電源管理總線,確保處理器無論在任何時候,以任何頻率操作,都可采用最低的電壓,以便將動態(tài)能耗降至最低。

PowcrWise技術也可為處理器的電位阱提供偏壓。由于供電電壓Vdd已調低:以減少動態(tài)損耗,晶體管的閾值電壓也必須調低,以確保驅動電壓可以保持在較高的水平,但缺點是漏電與靜態(tài)功率損耗會增加。我們只要為電位阱提供反向偏壓,漏電便會減少。此外,以同—供電電壓(Vdd)為例來說,我們也叫為電位阱提供正向偏壓,以提高驅動電壓。

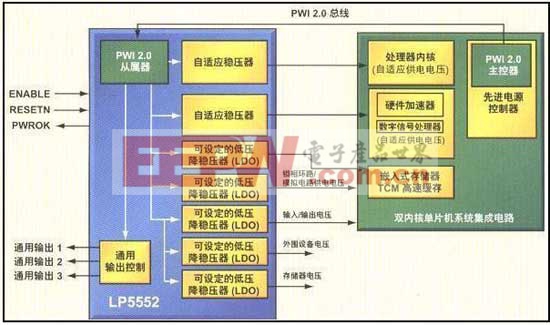

可以支持PowcrWise閉環(huán)AVS功能的標準系統(tǒng)配置必須有以下的基本元件:內置于處理器之內的先進電源控制器、設有PWI從屬器的電源管理集成電路,以及將兩者連接一起的雙線PWI串行總線。電源管理集成電路負責為處理器提供個同的電壓,電壓大小則由先進電源控制器內的PWI主控器負責調節(jié),辨法是由主控器將有關的命令傳往PWI從屬器,再由相關的電路進行調節(jié)。

先進電源控制揣負責接收主處理脂的命令,為電壓控制過程提供一個不受處理器影響的操作環(huán)境,以及實時跟蹤邏輯電路的操作速度。先進電源控制器永遠處于戒備狀態(tài),不斷監(jiān)測系統(tǒng)的一切參數(shù),例如,系統(tǒng)溫度、負載、瞬態(tài)、工藝及其他有關的變動都會受到監(jiān)測,每當先進電源控制器收到有關頻率即將轉變的消息,便會先行作出研判,以確定若以新頻率操作,系統(tǒng)最少需要多少供電才叫可穩(wěn)定操作。整個過程由閉環(huán)電路負責監(jiān)控,例如先進電源控制器先將電電調節(jié)命令經(jīng)由PWI接口傳送到PWI從屬器,然后再由伺服裝置將電壓凋節(jié)到適當?shù)乃健?/p>

圖3為典型的利用PowcrWise技術降低耗能的芯片LP5552所具結構示意框圖。其技術參數(shù)如下。

LP5552輸出數(shù)目為7.輸出電壓及電流有:2個降壓穩(wěn)壓器為0.8v to1.235v輸出電壓,800mA的輸出電流;5個降壓穩(wěn)壓器為0.8v to3.3v輸出電壓,高達250mA的輸出電流。輸入電壓范圍為2.7V至4.8V。接口為PWl 2.0。封裝為micro SMD-3。

3.2PowerWise技術應用

PowerWise技術是先進的能源管理解決方案,主要針對當前和未來受能源所限制的數(shù)字設備,適用于雙內核處理器、手機、便攜式收音機、個人數(shù)字助理、以電池供電的電子產(chǎn)品以及便攜式設備。可將數(shù)字處理器的能耗降低70%,從而延長電池壽命、支持更多功能和改善使用者的體驗。PowerWise采用自適應電壓調節(jié)(AVS)和閾值電壓調節(jié)等技術,將數(shù)字邏輯集成電路的工作和泄漏功耗自動降至最低,同時保持最小的系統(tǒng)開銷。

PowerWise 技術提供在單芯片系統(tǒng)和支持組件之間的一種優(yōu)化的閉環(huán)回路,而無需CPU干涉。嵌入式 PowerWise 技術因為可以合成,所以可不受處理器影響。

4、結束語-電源排序技術也是一種較為理想之節(jié)能方案

對于下不同類型的產(chǎn)品其節(jié)能技術方式也有所不同.而電源排序技術的應用也是一種較為理想之方案。因為在很多大功率系統(tǒng)中,空間和冷卻系統(tǒng)的成本都很高。因此,就任何POL轉換器而言,做到緊湊、高效率并具有低靜態(tài)電流以滿足新的“綠色”標準都是極端重要的。另外,很多微處理器和數(shù)字信號處理器(DSP)都需要一個內核電源和一個輸入/輸出(1/())電源,這些電源在啟動時必須排序。設計人員必須考慮加電和斷電操作時內核和I/O電壓源的相對電壓和時序,以符合制造商的性能規(guī)格要求.沒有恰當?shù)碾娫磁判颍涂赡艹霈F(xiàn)閉鎖或過大的電流消耗,這有可能導致微處理器I/O端口損壞,或存儲器、可編程邏輯器件(PLD)、現(xiàn)場可編程門陣列(FPGA)、數(shù)據(jù)轉換器等支持性器件的I/O端口損壞。

評論