基于PLL技術的電源管理設計

在PLL系統中,較高的VCO推壓意味著VCO電源噪聲的增加倍數更大。為盡可能降低對VCO相位噪聲的影響,需要低噪聲電源。

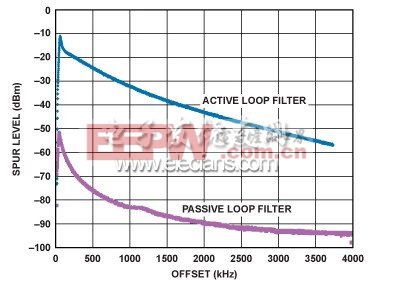

參考文獻3和參考文獻4提供了不同低壓差調節器(LDO)如何影響PLL相位噪聲的示例。例如,文獻中對ADP3334和ADP150 LDO為ADF4350供電時的性能進行了比較。ADP3334調節器的集成均方根噪聲為27 μV(40多年來,從10 Hz至100 kHz)。該結果可與ADF4350評估板上使用的LDO ADP150的9 μV比較。圖3中可以看出已測量PLL相位噪聲頻譜密度的差異。測量使用4.4 GHz VCO頻率進行,其中VCO推壓為最大值(表1),因此屬于最差情況結果。ADP150調節器噪聲足夠低,因此對 VCO噪聲的貢獻可以忽略不計,使用兩節(假定無噪聲)AA電池重復測量可確認這一點。

圖3.使用ADP3334和ADP150LDO對(AA電池)供電時ADF4350在4.4GHz下的相位噪聲比較

圖3強調了低噪聲電源對于ADF4350的重要性,但對電源或 LDO的噪聲該如何要求呢?

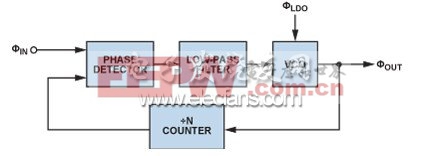

與VCO噪聲類似,LDO的相位噪聲貢獻可以看成加性成分LDO(t), 如圖4所示。再次使用VCO超額相位表達式得到:

或者在頻域中為:

其中vLDO(f)是LDO的電壓噪聲頻譜密度。

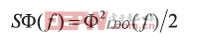

1 Hz帶寬內的單邊帶電源頻譜密度SΦ(f)由下式得出:

以dB表示時,用于計算電源噪聲引起的相位噪聲貢獻的公式如下:

(1)

其中 L(LDO)是失調為f時,調節器對VCO相位噪聲(以dBc/Hz表示)的噪聲貢獻; f; Kpushing是VCO推壓系數,以Hz/V表示;vLDO(f)是給定頻率偏移下的噪聲頻譜密度,以V/√Hz表示。

圖4.小信號加性vco電源噪聲模型

在自由模式VCO中,總噪聲為 LLDO值加VCO噪聲。以dB表示則為:

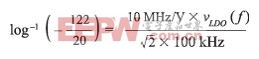

例如,試考慮推壓系數為10 MHz/V、在100 kHz偏移下測得相位噪聲為–116 dBc/Hz的VCO:要在100 kHz下不降低VCO噪聲性能,所需的電源噪聲頻譜密度是多少?電源噪聲和VCO噪聲作為方和根添加,因此電源噪聲應比VCO噪聲至少低6 dB,以便將噪聲貢獻降至最低。所以LLDO應小于–122 dBc/Hz.使用公式1,

求解vLDO(f),

在100 kHz偏移下,vLDO(f) = 11.2 nV/√

給定偏移下的LDO噪聲頻譜密度通常可通過LDO數據手冊的典型性能曲線讀取。

當VCO連接在負反饋PLL內時,LDO噪聲以類似于VCO噪聲的方式通過PLL環路濾波器進行高通濾波。因此,上述公式僅適用于大于PLL環路帶寬的頻率偏移。在PLL環路帶寬內,PLL可成功跟蹤并濾 LDO噪聲,從而降低其噪聲貢獻。

LDO濾波

要改善LDO噪聲,通常有兩種選擇:使用具有更少噪聲的LDO,或者對LDO輸出進行后置濾波。當無濾波器的噪聲要求超過經濟型LDO的能力時,濾波選項可能是不錯的選擇。簡單的LC π 濾波器通常足以將帶外LDO噪聲降低20 dB(圖5)。

圖5.用于衰減LDO噪聲的LCπ濾波器

選擇器件時需要非常小心。典型電感為微亨利范圍內(使用鐵氧體磁芯),因此需要考慮電感數據手冊中指定的飽和電流(ISAT), 作為電感下降10%時的直流電平。VCO消耗的電流應小于ISAT. 有效串聯電阻(ESR) 也是一個問題,因為它會造成濾波器兩端的IR壓降。對于消耗300 mA直流電流的微波VCO,需要ESR小于0.33 ?的電感,以產生小于100 mV的IR壓降。較低的非零ESR還可抑制濾波器響應并改善LDO穩定性。為此,選擇具有極低寄生ESR的電容并添加專用串聯電阻可能較為實際。上述方案可使用可下載的器件評估器如NI Multisim?在SPICE 中輕松實現仿真。 .

評論