電源時序控制

上電考量

本文引用地址:http://www.104case.com/article/177108.htm隨著集成電路(IC)時代的到來,許多功能模塊被集成到一個IC中,因而需要利用多個電源為這些模塊供電。這些電源的電壓有時候相同,但更多時候是不同的。市場上的片上系統(SoC) IC越來越多,這就產生了對電源進行時序控制和管理的需求ADI公司的數據手冊通常會提供足夠的信息,指導設計工程師針對各IC設計正確的上電序列。然而,某些IC明確要求定義恰當的上電序列。對于ADI公司的許多IC,情況都是如此。在使用多個電源的IC中,如轉換器(包括模數轉換器ADC和數模轉換器DAC)、數字信號處理器(DSP)、音頻/視頻、射頻及許多其它混合信號IC中,這一要求相當常見。本質上,包含某種帶數字引擎的模擬輸入/輸出的IC都屬于這一類,可能需要特定的電源時序控制。這些IC可能有獨立的模擬電源和數字電源,某些甚至還有數字輸入/輸出電源,詳情請參閱下文討論的具體示例。

本應用筆記討論設計工程師在新設計中必須考慮的某些更微妙的電源問題,特別是當IC需要多個不同的電源時。目前,一些較常用的電源電壓是:+1.8 V、+2.0 V、+2.5 V、+3.3 V、+5 V、-5 V、+12 V和-12 V.

ADI公司在全球銷售的產品超過10,000種,但本應用筆記的討論范圍僅限于幾款ADC.不過,這些電源時序考慮實際上可以應用于ADI公司的任何混合信號IC.

PULSAR ADC示例--絕對最大額定值

ADI公司的所有數據手冊都含有絕對最大額定值(AMR)部分,它說明為避免造成破壞,對引腳或器件可以施加的最大電壓、電流或溫度。

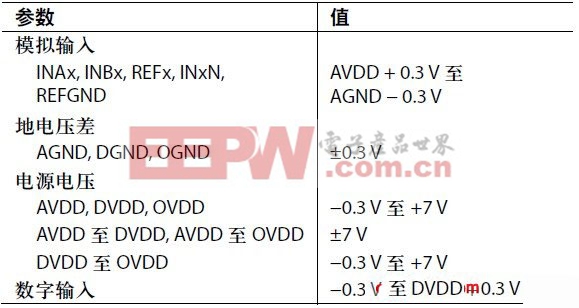

AD7654 PulSAR 16位ADC是采用三個(或更多)獨立電源的混合信號ADC的范例。這些ADC需要數字電源(DVDD)、模擬電源(AVDD)和數字輸入/輸出電源(OVDD)。它們是ADC,用于將模擬信號轉換成數字代碼,因此需要一個模擬內核來處理傳入的模擬輸入。數字內核負責處理位判斷過程和控制邏輯。I/O內核用于設置數字輸出的電平,以便與主機邏輯接口(電平轉換)。ADC的電源規格可以在相應數據手冊的絕對最大額定值部分找到。表1摘自AD7654 (Rev. B)數據手冊的絕對最大額定值部分。

表1. AD7654的絕對最大額定值(Rev. B)

注意,表1中所有三個電源的范圍都是-0.3 V至+7 V.相對于DVDD和OVDD,AVDD的范圍是+7 V至-7 V,這就確認了AVDD和DVDD無論哪一個先上電都是可行的。此外,AVDD和OVDD無論哪一個先上電也是可行的。然而,DVDD與OVDD之間存在限制。技術規格規定,OVDD最多只能比DVDD高0.3 V,因此DVDD必須在OVDD之前或與之同時上電。如果OVDD先上電(假設5 V),則DVDD在上電時比OVDD低5 V,這不符合絕對最大額定值要求,可能會損壞器件。

模擬輸入INAx、INBx、REFx、INxN和REFGND的限制是:這些輸入不得超過AVDD + 0.3 V或AGND ? 0.3 V.這說明,如果模擬信號或基準電壓源先于AVDD存在,則模擬內核很可能會上電到閂鎖狀態。這通常是一種無損狀況,但流經AVDD的電流很容易逐步升至標稱電流的10倍,導致ADC變得相當熱。這種情況下,內部靜電放電(ESD)二極管變為正偏,進而使模擬電源上電。為解決這個問題,輸入和/或基準電壓源在ADC上電時應處于未上電或未連接狀態。

同樣,數字輸入電壓范圍為?0.3 V至DVDD + 0.3 V.這說明,數字輸入必須小于DVDD + 0.3 V.因此,在上電時,DVDD必須先于微處理器/邏輯接口電路或與之同時上電。

與上述模擬內核情況相似,這些引腳上的ESD二極管也可能變為正偏,使數字內核上電到未知狀態。

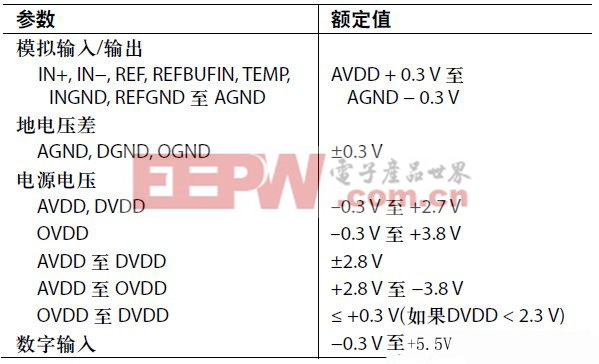

AD7621、AD7622、AD7623、AD7641和AD7643等PulSARADC速度更快,是該系列的新型器件,采用更低的2.5 V電源(AD7654則采用5 V電源)。AD7621和AD7623具有明確規定的上電序列。表2摘自AD7621 (Rev. 0)數據手冊的絕對最大額定值部分。

表2. AD7621的絕對最大額定值(Rev. 0)

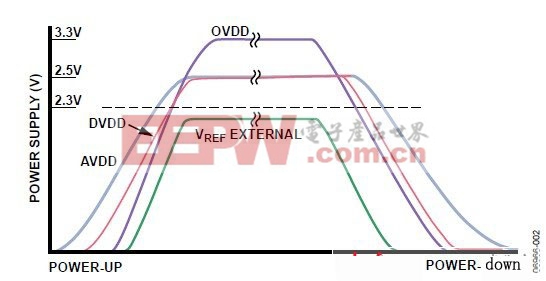

同樣,OVDD與DVDD之間存在限制。絕對最大額定值規定:OVDD必須小于或等于DVDD + 0.3 V,而DVDD則必須小于2.3 V.一旦DVDD在上電期間達到2.3 V,該限制便不再適用。如果不遵守該限制,AD7621(和AD7623)可能會受損(見圖1)。

因此,一般上電序列可能是這樣的:AVDD、DVDD、OVDD、VREF.但是,每個應用都不一樣,需要具體分析。注意,器件關斷與器件上電同樣重要,切記遵守同樣的規格要求。圖1所示為AD7621的典型上電/關斷序列。

圖1. 可能的上電/關斷序列-AD7621 (Rev. 0)

對于這些ADC,模擬輸入和基準電壓源的情況與上文所述相同。對任何模擬輸入引腳施加電壓都可能導致ESD二極管變為正偏,從而使模擬內核上電到未知狀態。

這些ADC的數字輸入和輸出略有不同,因為這些器件應支持5 V數字輸入。這些ADC是AD7654的速度升級版本,數字輸入和輸出均與OVDD電源相關,因為它能支持更高的3.3 V電壓。

注意:數字輸入限制為5.5 V,而AD7654則為DVDD + 0.3 V.

∑-△型ADC示例。

AD7794 ∑-△型24位ADC是另一個很好的例子。表3摘自AD7794 (Rev. D)數據手冊的絕對最大額定值部分。

表3. AD7794的絕對最大額定值(Rev. D)

該ADC的問題與基準電壓有關,它必須小于AVDD + 0.3 V.

因此,AVDD必須先于基準電壓或與之同時上電。

電源時序控制器

ADI公司提供許多電源時序控制器件。一般而言,其工作原理是:當第一個調節器的輸出電壓達到預設閾值時,就會開始一段時間延遲,延遲結束后才會使能后續調節器上電。關斷期間的程序與此相似。時序控制器也可以用于控制電源良好信號等邏輯信號的時序,例如:對器件或微處理器施加一個復位信號,或者簡單地指示所有電源均有效。

建議

采用分立設計變得越來越困難,解決之道就是采用電源時序控制IC,只要改變一下代碼就能改變上電順序,而不用變更PCB布局布線。

評論