數字電源控制器 UCD3138 的 Single Frame 和前饋功能說明

圖 4:前饋輸出最終與環路輸出相乘

本文引用地址:http://www.104case.com/article/175998.htm前饋功能的硬件設計主要包含了輸入電壓的檢測電路,在第一章曾有描述,在此不再贅述。軟件設計主要包含了Vref(DAC)值的配置、Kc 的配置和前饋功能的啟用設置。

1)Vref(DAC)值的配置

如下函數實現了根據v_input_error 的大小對Vref(DAC)值的更新。v_input_error 為當前采集的輸入電壓與前一次采集到的輸入電壓的差值。該函數包含在一個狀態機中,100us 執行一次,將連續執行300 次,以保證在使能前饋功能之前Vref(DAC)近似等于當前輸入電壓。

if(v_input_error > 10)

{

if(FeCtrl2Regs.EADCDAC.bit.DAC_VALUE > 3000) //can not lower than 35V;

{FeCtrl2Regs.EADCDAC.bit.DAC_VALUE = FeCtrl2Regs.EADCDAC.bit.DAC_VALUE - 1;}

}

else if(v_input_error -10)

{

if(FeCtrl2Regs.EADCDAC.bit.DAC_VALUE 14000) //can not higher than 80V;

{FeCtrl2Regs.EADCDAC.bit.DAC_VALUE = FeCtrl2Regs.EADCDAC.bit.DAC_VALUE + 1; }

}

如果誤差很小,即輸入電壓已經穩定,則系統軟件準備開啟前饋功能并隨后進入正常運行的狀態機。

if ( abs(v_input_error) 10) //Vin error is small

{

supply_state = STATE_REGULATED;

Filter0Regs.FILTERCTRL.bit.OUTPUT_MULT_SEL =2;//Enable Feed Forward

}

2)Kc 值的配置

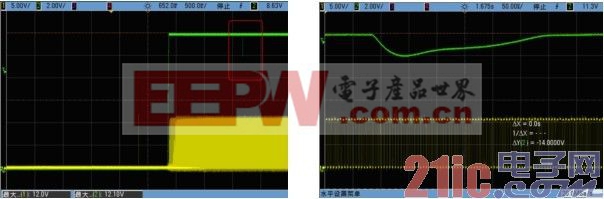

在輸入電壓穩定的情況下,如果Kc 直接配置到0.5 到0.7 的某個值,則此時啟用前饋功能會影響正常環路的輸出,造成輸出電壓出現跌落。如下圖5 所示。

圖 5:Kc 啟用不當造成輸出有跌落

跌落的原因是因為此時環路的正常輸出被突然乘以Gain=Kc=0.5~0.7,所以占空比會立即被限制,輸出電壓出現跌落。直到環路經過多個周期后再將占空比展開到正常大小,輸出電壓才恢復到正常值。

因此,在實際應用中需要將Kc 由1 慢慢減小到需求的值(在本文涉及的硬全橋軟件中選擇Kc 為0.7)。另,在實際設計中使用Filter2 實現非線性增益和Kc 的設置,因此軟件配置如下。

Uint32 filter2_kc;

int filter2_kc_step = 0x200;

inline void handle_regulated_state(void)

{

filter2_kc = Filter2Regs.FILTERPRESET.bit.PRESET_VALUE;// It is Kc

if(Filter2Regs.FILTERPRESET.bit.PRESET_VALUE > 0x5A0000)

{

Filter2Regs.FILTERPRESET.bit.PRESET_VALUE = filter2_kc - filter2_kc_step;

Filter2Regs.FILTERPRESET.bit.PRESET_EN = 1;

}

}

其中,handle_regulated_state 為軟件狀態機中的一個狀態,每100us 執行一次。通過這樣一個循環函數就可以保證Kc 是以步進的形式由1 配置到0.7(0x5A0000/0x7FFFFF=0.7),防止了輸出電壓出現跌落。

3)前饋功能的啟用

經過上述完善的預先配置后,可以啟用前饋功能,啟用后KC 從1 慢慢開始減小。啟動的設置是通過下面代碼實現的。“OUTPUT_MULT_SEL”位用來選擇與環路輸出相乘的值,以決定最后的占空比。當設置為2時,將選擇前饋的輸出與環路輸出相乘,即啟動了前饋。

Filter0Regs.FILTERCTRL.bit.OUTPUT_MULT_SEL =2;

評論