BU-61580芯片與PPC處理器的接口設(shè)計(jì)與分析

外設(shè)配置在PCI空間可以解決配置在CS2/CS3空間中的問(wèn)題,但是需要將PCI轉(zhuǎn)換成ISA總線接口。這種設(shè)計(jì)方案采用BU-61580的16緩沖方式下的非零等待方式,16透明方式及DMA方式比較合適。在實(shí)際應(yīng)用中具體選用BU-61580的16緩沖方式下的非零等待方式,16透明方式及DMA方式要根據(jù)具體系統(tǒng)架構(gòu)來(lái)決定選擇那種方式,以下對(duì)這幾種訪問(wèn)方式作進(jìn)一步的詳細(xì)介紹。本文引用地址:http://www.104case.com/article/175852.htm

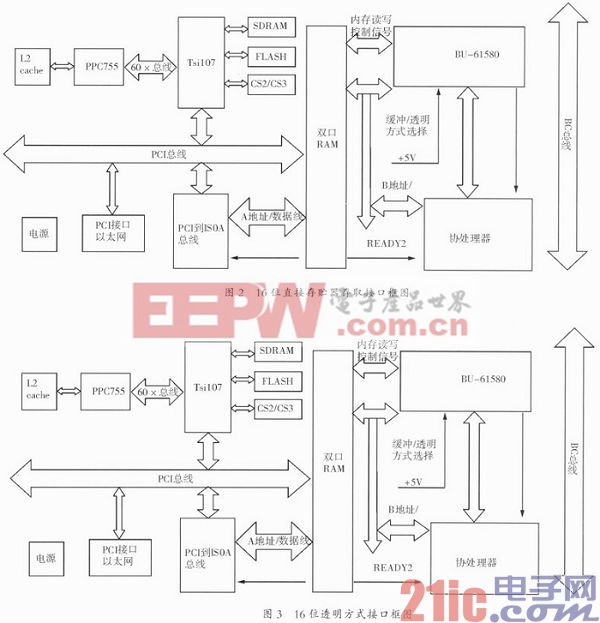

圖2為BU-61580和PPC處理器DMA方式的典型接口電路。當(dāng)傳輸?shù)臄?shù)據(jù)量大于64 Kbyte時(shí)緩沖方式和透明方式都不能滿(mǎn)足要求,由于BC總線控制器和PPC755訪問(wèn)BU-61580不同步,必然會(huì)有對(duì)內(nèi)存訪問(wèn)的總線沖突與仲裁問(wèn)題,如果用PPC755處理器與BU-61580直接用DMA方式進(jìn)行連接,PPC55的運(yùn)行效率會(huì)受到嚴(yán)重的影響。圖2中協(xié)處理器解決此問(wèn)題,協(xié)處理器在中斷產(chǎn)生后進(jìn)行給雙口RAM寫(xiě)數(shù)或者讀數(shù),避免了BU-61580芯片內(nèi)部共享內(nèi)存訪問(wèn)的競(jìng)爭(zhēng),PPC755訪問(wèn)BU-61580協(xié)議芯片的數(shù)據(jù)轉(zhuǎn)換到與協(xié)處理器訪問(wèn)雙口RAM的數(shù)據(jù)。這種方法對(duì)軟件初始化BU-61580芯片RT內(nèi)存管理比較靈活。

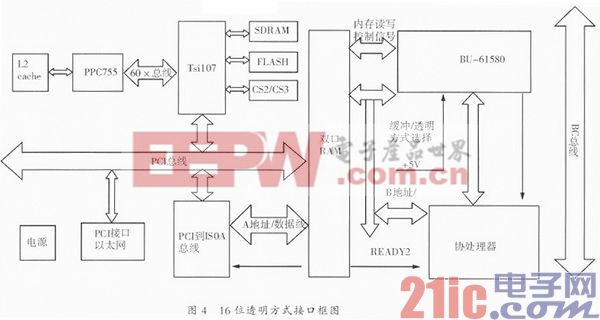

圖3和圖4為BU-61580和PPC755處理器透明方式和緩沖方式的典型接口電路,兩種方式都需要將BU-61580的輸出握手信號(hào)連接到PPC755處理器的READY信號(hào)。透明方式比緩沖方式的優(yōu)點(diǎn)就是外部緩沖RAM可擴(kuò)展到64K byte,缺點(diǎn)就是硬件上需要增加物理隔離,同時(shí)對(duì)外部緩沖RAM的訪問(wèn)需要BU-61580的內(nèi)存讀寫(xiě)控制信號(hào)參與。在傳輸數(shù)據(jù)量比較少,BU-61580內(nèi)部的4Kbyte RAM足夠用時(shí),可選用16位緩沖器接口方式。

由于BC總線控制器和PPC755訪問(wèn)BU-61580不同步,必然會(huì)有總線沖突與仲裁問(wèn)題,當(dāng)發(fā)生訪問(wèn)共享內(nèi)存沖突時(shí),硬件上READY信號(hào)就會(huì)加入自動(dòng)等待。這兩種接口設(shè)計(jì)方法可以將INT中斷信號(hào)連接到PPC755處理器的中斷控制器上,在中斷服務(wù)程序中處理數(shù)據(jù),但中斷對(duì)PPC755處理器開(kāi)銷(xiāo)比較大,一般不推薦直接使用。通常采用定時(shí)查詢(xún)的方式,可以利用BU-61580RT提供的全局雙緩存存儲(chǔ)器管理機(jī)制,通過(guò)1#配置寄存器的第13位(CURREENT AREA B/~A)來(lái)選擇激活部分。這樣,在任意時(shí)刻,有一“激活”的堆棧指針、堆棧區(qū)域、查詢(xún)表以及若干數(shù)據(jù)塊用于1553消息處理,另外一套數(shù)據(jù)結(jié)構(gòu)處于“非激活”狀態(tài)。“激活”與“非激活”RAM區(qū)域都可被主機(jī)程序訪問(wèn)。

4 結(jié)束語(yǔ)

本文介紹了BU-61580芯片RT方式下與PPC755的幾種存儲(chǔ)器接口方式。根據(jù)處理器的架構(gòu)和系統(tǒng)的實(shí)際應(yīng)用對(duì)幾種存儲(chǔ)器接口方式進(jìn)行了分析說(shuō)明,文中提出的幾種接口方式已經(jīng)在實(shí)際工程產(chǎn)品中得到應(yīng)用,具有一定的推廣和借鑒意義。

評(píng)論