動態掃描數字鐘電路設計與制作

0 引言

本文引用地址:http://www.104case.com/article/174976.htm在電子技術實驗教學中,構建的電路設計理念,提高的電路設計能力,是教學的根本目的和核心內容.數字鐘電路的設計包括了時序邏輯電路.組合邏輯電路.數碼管顯示電路和脈沖信號產生電路等內容,內容涉及面寬.綜合性強,是電子技術自主性實驗教學的典型案例.文中采用了石英晶體振蕩器電路.計數電路.動態掃描及譯碼驅動電路.顯示電路和時鐘校正電路,來實現該電路.

1 系統設計方案

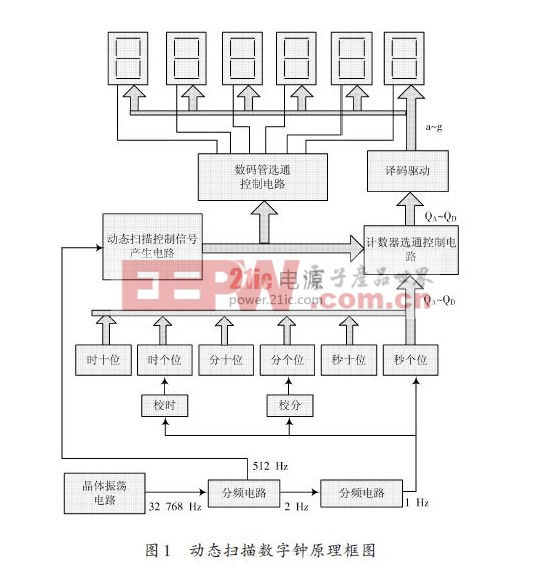

本次設計的數字鐘,實現對時.分.秒的數字顯示,周期為24 h,顯示滿刻度為23 時59 分59 秒,并具有校時功能.電路主要采用中規模CMOS集成電路,采用電池作電源,通過共陰極LED 數碼管顯示時鐘.該系統由秒脈沖產生模塊.計數器模塊.譯碼顯示電路模塊.動態掃描模塊.校時模塊組成.其中秒脈沖產生模塊由晶體振蕩器電路和兩個分頻器電路組成,動態掃描模塊由動態掃描控制信號產生電路.計數器選通控制電路和數碼管選通控制電路三部分組成,系統組成框圖如圖1所示.

1.1 秒脈沖產生電路

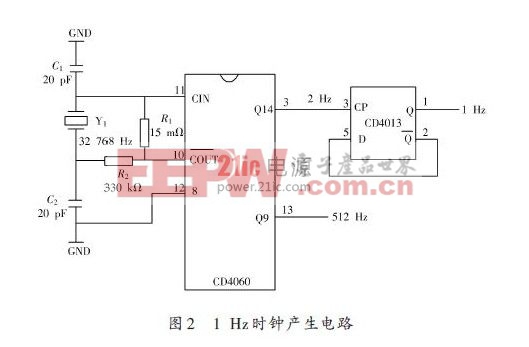

秒脈沖信號由石英晶體振蕩器產生,由于晶體振蕩器輸出頻率較高,為了得到1 Hz 的秒信號,需要對振蕩器的輸出信號進行分頻.通常的分頻器采用多級二進制計數器來實現.將32 768 Hz 的高頻方波信號經32 768(215)次分頻后得到1 Hz的方波信號供秒計數器進行計數,即實現該分頻功能的計數器相當于15 級二進制計數器.

本次設計采用CD4060 來構成14 級2 分頻電路.

CD4060的9腳.10腳.11腳內含兩個非門電路,1腳輸出12分頻信號,2腳輸出13分頻信號,3腳輸出14分頻信號.利用CD4060的兩個非門和32768Hz的晶振構成32 768 Hz 的振蕩器,然后通過CD4060 進行214 分頻得到2 Hz的信號,再經過D觸發器CD4013進行一次二分頻即可得到1 Hz的秒脈沖.電路圖如圖2所示.

1.2 計數器設計

計數器電路用來完成60 秒60 分及24 小時的計數工作,且秒計數器的進位脈沖作為分計數器的輸入脈沖,同理分計數器的進位脈沖作為小時計數器的輸入脈沖.“ 秒”.“ 分”.“ 時”計數器電路采用同步加計數器CD4518來完成.

(1)CD4518雙BCD同步加計數器

CD4518 是一只雙BCD 十進制計數器,它含有2 個獨立的計數單元,有2個計數脈沖輸入端,上升沿觸發端CP 和下降沿觸發端EN,若用CP 來觸發,則EN 接高電平,且為上升沿觸發;若用EN 來觸發,則CP 接低電平,且為下降沿觸發;有4個輸出端QD~QA,一個清零端.

CD4511的引腳圖如圖3所示.其中:

CP:時鐘輸入端,上升沿觸發;

EN:時鐘輸入端,下降沿觸發;

R:復位端,高電平時計數器=0;

QD~QA:計數值十進制輸出端;

UDD:正電源輸入端(3~15 V);

USS:電源參考地.

分頻器相關文章:分頻器原理 塵埃粒子計數器相關文章:塵埃粒子計數器原理 三維掃描儀相關文章:三維掃描儀原理

評論