一種夾層電阻結構及其應用

1 引言

本文引用地址:http://www.104case.com/article/174851.htm在集成電路的線路設計中,特別是模擬電路的設計中,不可避免地都會需要用到電阻。對于低阻值的應用,一般可以用鋁線電阻、多晶電阻、N+電阻或者P+電阻等實現。對于更大一點的電阻,則可以用N阱電阻、P阱電阻或者高阻多晶等實現。對于更高阻值要求,或者阻值要求高但是占用面積要小且精度要求不高,這時候可以用倒比的MOS管或者夾層電阻來實現。顧名思義,夾層電阻就是被其他層次夾在中間的電阻,夾層電阻的方塊阻值一般在5~50 kΩ,隨著電壓的提高,還可以到100 kΩ或更高。

2 夾層電阻結構及原理特性分析

2.1 夾層電阻的結構

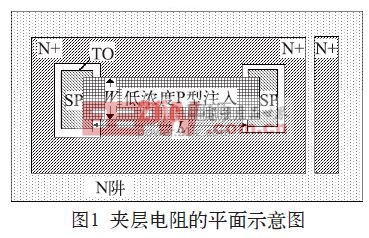

在集成電路工藝中,實現夾層電阻有很多種方法。本文研究的夾層電阻就是其中的一種,它不需要通過額外增加光刻MASK層就能實現。圖1為該夾層電阻的平面示意圖。

圖1中,夾層電阻區為低濃度的P型注入區,它主要利用工藝中的現有層次實現,比如Pbase層或者Pbody層。該P型夾層電阻區被N+和N阱完全包圍,因此該結構就是一個被N+和N阱兩個層次夾在中間的P型夾層電阻。

2.2 夾層電阻的特性

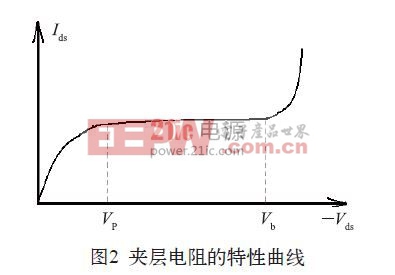

夾層電阻的優勢是阻值很高,缺點是對電壓比較敏感。對該夾層電阻進行I-V掃描,起始電壓為0 V,步進為0.5 V,結果發現如下特性:當電阻兩端電壓從0開始增加時,夾層電阻的阻值迅速上升,但是到電壓超過4 V左右后,電阻阻值雖然還是繼續增加,但是此時呈現出線性上升的特性,即電阻跟隨電壓呈比例地上升,當電壓到14~15 V左右時,電阻開始急劇減小,呈現出擊穿效應。把上述電阻測試時的I-V數值進行曲線擬合,得到圖2.

圖2中,拐點Vp約為4 V,拐點Vb約為14~15 V.

2.3 夾層電阻的原理分析

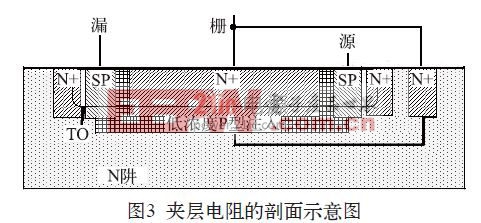

觀察該曲線,發現它很像MOS管的輸出特性曲線。進一步分析其縱向結構發現,該夾層電阻實際上可以理解成一個P溝道的JFET管(結型場效應管),它的縱向剖面示意圖如圖3所示。

圖3中,JFET管的溝道區為低濃度的P型注入區,P型溝道被N+和N阱上下夾住,因此可以把N+和N阱看成JFET管的柵極(Gate),把兩個SP注入區一個看成JFET管的源端(Source),另一個看成JFET管的漏端(Drain)。

因此在圖2中,拐點Vp就是該P溝道JFET管的夾斷電壓,當-Vds電壓超過Vp后,JFET管產生夾斷,源漏電流開始趨于穩定。拐點Vb為該P溝道JFET管的擊穿電壓,當-Vds電壓大于Vb后,JFET管產生擊穿,Ids增大。

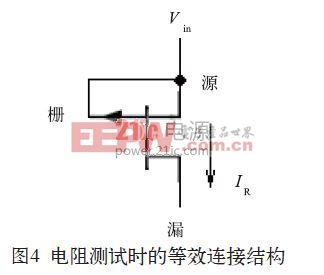

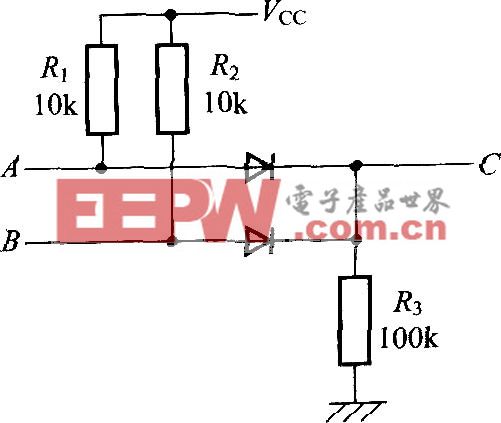

在前面的夾層電阻測試時,實際上是把PJFET管的柵端(Gate)和源端(Source)短接,形成了圖4所示的連接結構。

由圖4可知,只要把該JFET管的柵源短接且都接到輸入工作電壓Vin上,則當電壓在Vp和Vb之間變化時(即Vp

一般來說,Vp在3~4 V左右,而Vb可以在10~15 V左右甚至更高,當然,由于不同工藝間的差異,Vp和Vb的大小會有所不同。

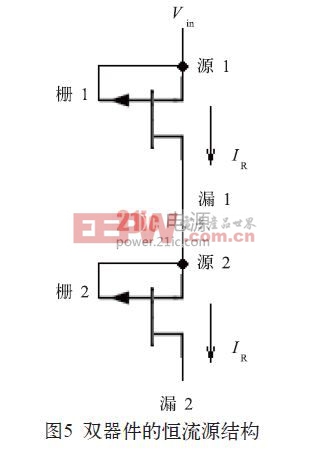

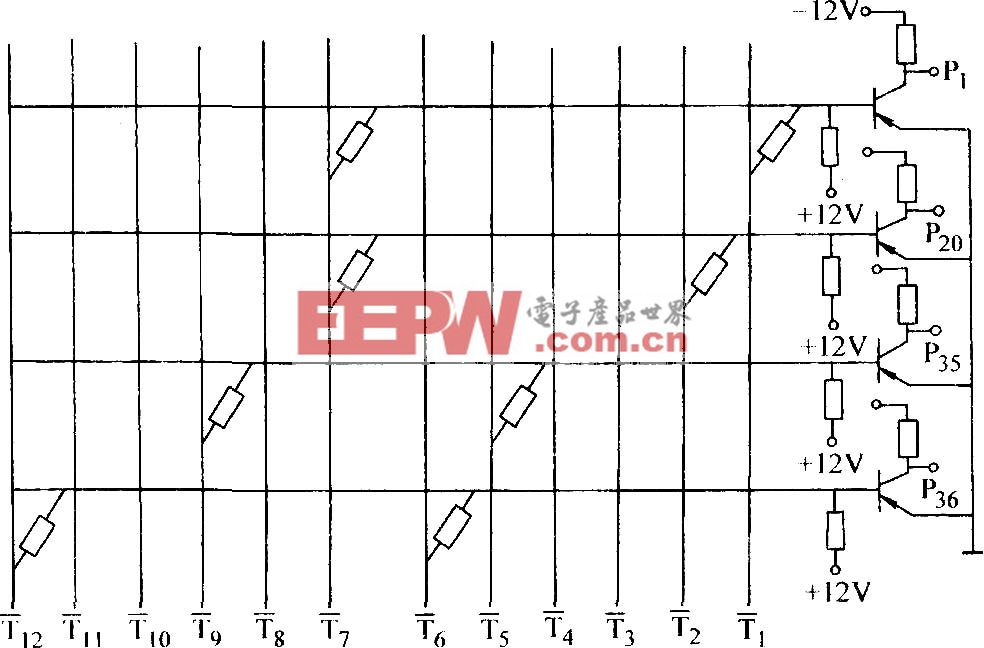

上述單器件電流源能滿足輸入電壓在4~15 V左右之間變化時,輸出恒定電流。為了獲得更寬的電壓范圍,需要對上述電路進行改進,如圖5.

電阻相關文章:電阻的作用居然有這么多,你造嗎

光敏電阻相關文章:光敏電阻工作原理

評論