TMS320F241型DSP的SPI口EEPROM擴展

摘要:敘述了TI公司的TMS320F241型DSP的串行外設接口(SPI)擴展EEPROM的軟、硬件實現方法。

關鍵詞:DSP SPI EEPROM X5043

1.引言

TMS320F241型DSP是目前應用比較廣泛的一款定點DSP,它具有20MIPS的指令執行速度,強大的內部事件管理器、I/O端口和其他外圍設備。其中,串行外設接口(SPI)是一個高速同步串行輸入/輸出(I/O)端口,它允許一個具有可編程長度(1到16位)的串行位流,以可編程的位傳送速率從設備移入或移出。SPI通常用于DSP控制器和外部器件或其它控制器間的通訊。

在開發DSP系統時,某些情況下會讀取或者存儲一些定值,這時我們就需要擴展EEPROM。具有SPI接口的串行EEPROM均可被TMS320F241直接邏輯擴展,方便易行。X5043是Xicor公司最高時鐘速率為3.3MHz帶有塊鎖保護的4Kbits的CMOS串行EEPROM。該器件內部組織陣列是X8位,具有串行外圍接口(SPI)和軟件協議的特點,允許在簡單的四線總線上工作;該器件利用Xicor專有的直接寫入晶片提供最小為10萬次擦寫和最少100年的數據保存期。

2.硬件設計

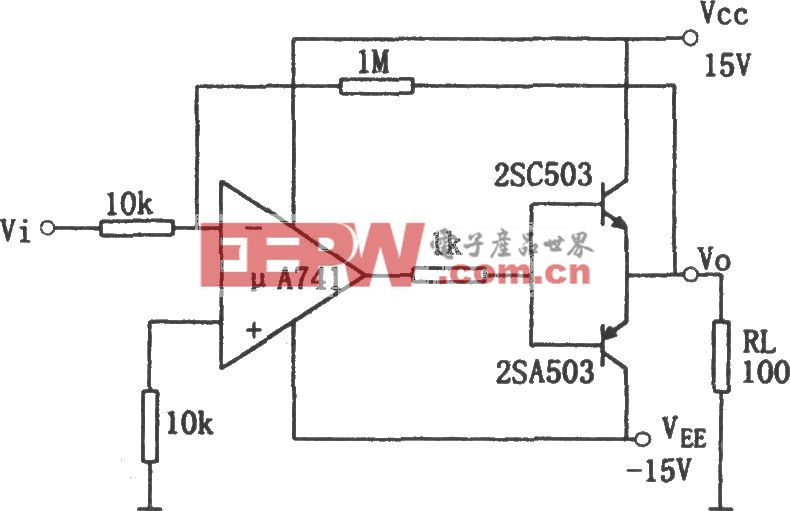

X5043與TMS320F241型DSP的連接關系如圖1所示。DSP作為主控制器,工作于主模式下,SPISIMO為DSP的數據發送端,連接到X5043的數據接收端(SI);SPISOMI為DSP的數據接收端,連接到X5043的數據發送端(SO);SPISTE配置成I/O口連接到X5043的片選端(/CS);SPICLK為SPI數據傳送的時鐘信號,連接到X5043的串行時鐘端(SCK),串行時鐘由DSP控制。DSP的數據在SPISIMO引腳上輸出并從SPISOMI上鎖存, DSP通過寫入SPIDAT寄存器的數據啟動SPICLK串行時鐘信號從而啟動數據傳送,當8位串行位流傳送完畢后,SPICLK信號中止,傳送結束。

3.軟件設計

3.1工作模式的選擇

TMS320F241的SPI接口有可選擇的四種不同的時鐘模式,如何選擇時鐘模式是它與各種擴展SPI接口器件實現時鐘同步的關鍵。X5043的數據在時鐘下降沿從SO引腳上輸出并在時鐘上升沿從SI引腳上鎖存。讀操作時,在其從SI引腳輸入的最低位地址所對應的時鐘下降沿,其SO引腳開始輸出數據,如圖5所示。

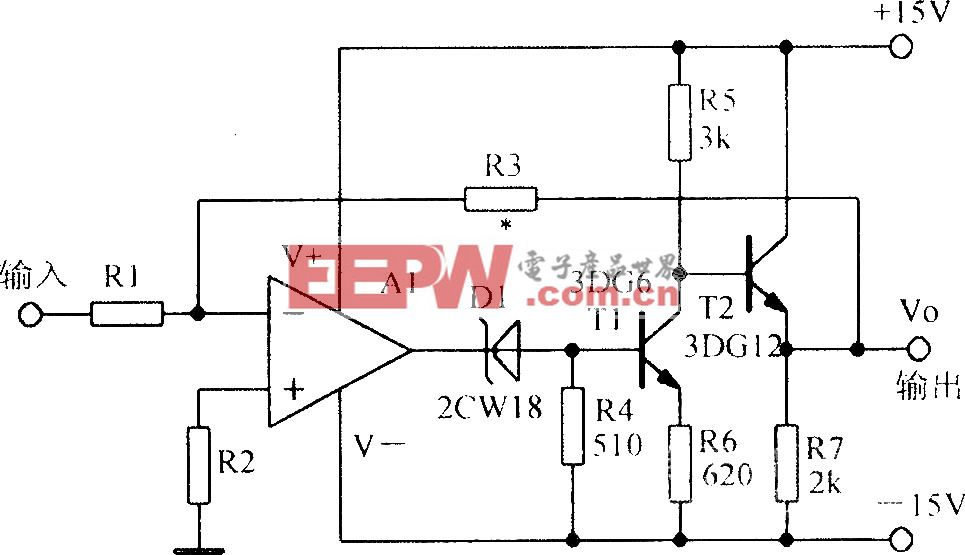

作為主器件的DSP可以選擇 ‘上升沿,無延時’和‘上升沿、有延時’兩種時鐘工作模式。‘上升沿,無延時’模式與X5043的工作模式一致,數據在SPICLK信號的時鐘上升邊沿(從低電平到高電平)從移位寄存器移出在SI引腳上鎖存,在時鐘下降邊沿(從高電平到低電平)從SO引腳上輸出的數據鎖存到移位寄存器中。‘上升沿,有延時’模式如圖4所示,數據在SPICLK信號上升沿前半個周期從移位寄存器移出,在緊接著的上升邊沿在SI引腳上鎖存,在時鐘下降邊沿(從高電平到低電平)從SO引腳上輸出的數據鎖存到移位寄存器中。

3.2波特率的選擇

SPI波特率可以由如下兩種情況計算得出:

(1)對于SPIBRR=3~127,波特率的計算公式為:

SPI波特率=CLKOUT/(SPIBRR+1)

(2)對于SPIBRR=0~2,波特率的計算公式為:

SPI波特率=CLKOUT/4

式中,CLKOUT=器件的CPU時鐘頻率;SPIBRR=主SPI器件中的SPIBRR內容。

X5043最大的SPI波特率為3.3MHz,若DSP的CPU時鐘頻率CLKOUT=16MHz,則:

最大的SPI波特率 =16106/(SPIBRR+1)≤3.3106Hz

SPIBRR≥4+9

3.3 DSP的數據傳輸格式

DSP中SPI有16位的發送和接收能力,且接收和發送均是雙緩沖。所有數據寄存器都是16位寬的,而X5043的地址、數據寄存器均是8位的,將DSP中SPI傳輸字符長度設置成8位寬。要向X5043存儲數據時,DSP將一個8位字節長度的數據寫入SPIDAT或SPITXBUF的高8位上如圖2所示,在時鐘信號的作用下,以左對齊方式發送,先發送數據的最高位。DSP接收一個8位字節長度的數據,是以右對齊方式接收如圖3所示,8位字節長度的數據寫入SPIDAT或SPIRXBUF 的低8位上。

3.4各控制寄存器設置

LDP #SPICCR>>7

SPLK #0007h,SPICCR

;復位SPI, 8個字符長度

SPLK #000Eh,SPICTL

;主模式,使能TALK,禁止SPI的中斷

;上升沿發送,下降沿接收,有延時

SPLK #000Fh,SPIBRR

;設置SPI的傳輸波特率

SPLK #0087h,SPICCR

;SPI準備好發送或接收下一字符

3.5程序設計

RAM塊中的變量定義:

.bss SPI_Xdata,1

;SPI數據傳輸暫存器

.bss address1,1

;EEPROM存儲器地址暫存器

.bss data1,1

;EEPROM存儲器數據暫存器

X5043存儲器地址:

WREN .set 0600h

;設置寫使能鎖存指令地址

WRDI .set 0400h

;復位寫使能鎖存指令地址

RSDR .set 0500h

;讀狀態寄存器指令地址

WRSR .set 0100h

;寫狀態寄存器指令地址

READh .set 0B00h

READl .set 0300h

;讀存儲器陣列數據指令地址

WRITEh .set 0A00h

WRITEl .set 0200h

;寫存儲器陣列數據指令地址

3.5.1 DSP的SPI數據發送、接收子程序代碼

XMIT_VALUE:

LDP #0

LACC SPI_Xdata

LDP #SPITXBUF>>7

SACL SPITXBUF

;寫需發送的值到SPI傳輸緩沖器

XMIT_RDY:

LDP #SPISTS>>7

BIT SPISTS,BIT6

BCND XMIT_RDY,NTC

;測試SPI_INT位,如果SPI_INT=0,則重復循環

;等待數據發送完畢進行下一步操作

LDP #SPIRXBUF>>7

LACL SPIRXBUF

;讀取數據清除SPI_INT標志位

LDP #0

SACL SPI_Xdata

;將接收的值存入數據傳輸暫存器

RET

3.5.2 X5043內部非易失性寫判斷子程序代碼

RSDR_WIP:

SPISTE_LOW

;置低SPISTE引腳,從而選通X5043

LDP #0

SPLK #RSDR,SPI_Xdata

CALL XMIT_VALUE

;寫讀狀態寄存器地址,高8位

SPISTE_HIGH

;置高SPISTE引腳,禁止X5043

LDP #0

BIT SPI_Xdata,BIT0

BCND RSDR_WIP,TC

;測試狀態寄存器WIP位。如果WIP=1,正在進行內部寫操作。

;等待內部寫操作完成進行下一步操作

RET

使用上述判斷子程序能夠保證X5043完成內部寫操作。向X5043存儲器陣列寫入數據時后面將跟隨一次非易失性寫操作。可以讀狀態寄存器檢查WIP位,若WIP為高則非易失性寫正在進行。X5043存儲器非易失性寫周期為10mS,也可以在一個寫操作完成后作一個大于10mS的延時,以保證X5043完成內部寫操作。

3.5.3向X5043 EEPROM存儲器陣列中寫數據

如圖4所示,向EEPROM存儲器陣列寫入任何數據之前,必須用WREN指令設置WEL位。首先將CS拉低,向器件輸入WREN指令,然后拉高/CS。再次拉低/CS并輸入WRITE指令,緊跟隨8位地址,然后是要寫入的數據。WRITE指令的位3是地址位A8,該位選擇陣列的高半部分或是低半部分。如果/CS在WREN和WRITE之間不變為高,則WRITE指令將被忽略。為了完成寫操作,在最后一個被寫入的數據字節的位0完成后/CS必須被拉高。如果它在任何其它時間被拉高,寫操作將不完成。

寫1個字節數據的程序代碼如下:

WRITE:

KICK_DOG

CALL RSDR_WIP

;讀狀態寄存器檢查WIP位

;寫WREN指令代碼段

SPISTE_LOW

;置低SPISTE引腳,從而選通X5043

LDP #0

SPLK #WREN,SPI_Xdata

CALL XMIT_VALUE

SPISTE_HIGH

;置高SPISTE引腳,禁止X5043

CALL RSDR_WIP

;讀狀態寄存器檢查WIP位

;寫WRITE指令/地址/數據代碼段

SPISTE_LOW

;置低SPISTE引腳,從而選通X5043

LDP #0

SPLK #WRITEl(h),SPI_Xdata

CALL XMIT_VALUE

;輸入寄存器指令

LDP #0

LACL address1

SACL SPI_Xdata

CALL XMIT_VALUE

;輸入寄存器地址

LDP #0

LACL data1

SACL SPI_Xdata

CALL XMIT_VALUE

;輸入寄存器數據

SPISTE_HIGH

;置高SPISTE引腳,禁止X5043

CALL RSDR_WIP

;讀狀態寄存器檢查WIP位,X5043完成內部非易失性寫

RET

3.5.4從X5043 EEPROM中讀取數據

如圖5所示,/CS只要拉低選中器件。8位READ指令送到器件,后面跟隨8位地址,就可以讀取指定地址下的EEPROM存儲器陣列中的數據。READ指令的位3選擇器件的高半部分或是低半部分。在READ指令碼和地址送出后,在選定地址的存儲在存儲器中的數據即在SO線上移出。讀操作由拉高/CS而終止。

讀1個字節數據的程序代碼如下:

READ:

KICK_DOG

CALL RSDR_WIP

;讀狀態寄存器檢查WIP位

SPISTE_LOW

;置低SPISTE引腳,從而選通X5043

LDP #0

SPLK #READl(h),SPI_Xdata

CALL XMIT_VALUE

;輸入寄存器指令

LDP #0

LACL address1

SACL SPI_Xdata

CALL XMIT_VALUE

;輸入寄存器地址

LDP #0

LACL data1

SACL SPI_Xdata

CALL XMIT_VALUE

;此data1無意義,使SPI口連續提供時鐘信號,使數據輸出

;輸出的數據存儲在SPI_Xdata中

SPISTE_HIGH

;置高SPISTE引腳,禁止X5043

RET

由于X5043是一個半雙工器件,在WRITE子程序中從SPIRXBUF中讀出來的數據是無效的,同時,在READ子程序中寫向SPITXBUF的data1數據也是無效的,只起啟動發送時鐘的作用。

4.結束語

DSP可以連續的向EEPROM中寫入多至16個字節的數據。唯一的限制是16個字節必須在同一頁中。一頁地址由[X XXXX 0000]開始,由[X XXXX 1111]結束。如果字節地址達到了頁中的最后字節而時鐘仍在繼續,則計數器將返轉至該頁的第一個地址并重寫前面已寫過的數據。在連續地提供時鐘脈沖的條件下儲存在存儲器地址處的數據可被連續地讀出。在每個數據字節被移出后,器件即自動將地址增加至下一個更高的地址。當達到最高的地址時,地址計數器即翻轉到地址00H,使讀周期無限制地連續下去。上面只給出了X5043單個字節的讀寫程序代碼,對于多個字節或一頁16個字節的讀寫程序代碼可根據單個字節的讀寫程序代碼進行擴展給出。

評論