無絕緣移頻自動閉塞系統中采集系統設計

(9)硬件實現的SPI,SMBus/I2C和兩個UART串行接口;

(10)通用的16位定時器;

(11)具有五個捕捉/比較模塊的可編程計數器/定時器陣列;

(12)片內看門狗定時器、VDD監視器和溫度傳感器。

C8051F020單片機的所有模擬和數字外設均可由用戶固件使能/禁止和配置。FLASH存儲器還具有在系統重新編程能力,可用于非易失性數據存儲,并允許現場更新805l固件。片內JTAG調試電路允許使用安裝在最終應用系統上的產品MCU進行非侵入式(不占用片內資源)、全速的在系統調試。該調試系統支持觀察和修改存儲器和寄存器,支持斷點、觀察點、單步及運行和停機命令。在使用JTAG調試時,所有的模擬和數字外設都可全功能運行。

采用開關網絡以硬件方式實現I/O端口的靈活配置,外設電路單元通過相應的配置寄存器控制交叉開關配置到所選擇的端口上,從而避免了固定方式I/O端口既占用引腳多,配置又不夠靈活的缺點。

4 EPM3256ATCl44-10簡介

EPM3256ATCl44-10是Altera公司MAX3000系列的CPLD芯片,其特點:是以多陣列矩陣(MAX)結構為基礎的高性能、低功耗的CMOS E2PROM器件,通過內置的JTAG(IEEE 1149.1)可實現在系統編程;內置符合IEEE 1149.1-1990標準的JTAG BST電路;是一款高密度器件,能提供5 000個可用門,256個宏單元,16個邏輯陣列塊,116個用戶I/O;引腳到引腳的邏輯延遲為5.5 ns,計數器工作頻率達172.4 MHz;多電壓I/O接口,使得核心工作在3.3 V時,I/0管腳可同時兼容5.0 V,3.3 V及2.5 V三種邏輯電平;遵守PCI規定,具有一10速度等級。

5 硬件設計原理

5.1 電源設計

該系統外部輸入電源為DC 48 V。DC 48 V電源經開關、防止接反二極管、濾波電容、熔斷電阻至電源濾波器,經濾波器濾波后送到兩個電源塊(48 V輸入,5 V輸出)。一個為輸入接口電路及通信接口電路供電,另一個經三端穩壓片(5 V輸入,3.3 V輸出)為內部執行電路及指示燈電路提供5 V及3.3 V電源。由于外圍接口電路采用單獨電源,與內部電路分開供電,實現了內部電路與接口電路的電源隔離,有效保護內部電路器件,提高了可靠性。

5.2 輸入信號處理

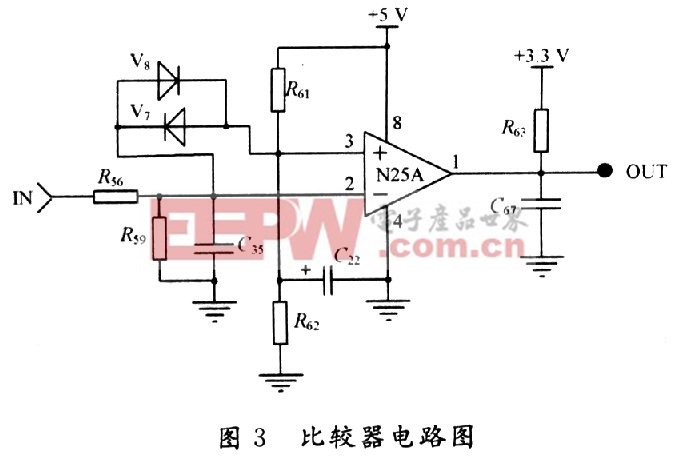

低頻、繼電器狀態及地址編碼等信號經光耦隔離后變為3.3 V方波或電平信號,送入主控單元。輸入模擬信號經變壓器隔離或升降壓、濾波、降壓電阻、瞬時過電壓保護等信號調理后,輸出信號為交變信號,而本系統中單片機內置ADC轉換輸入電壓范圍為0~3.3 V,因此在送入ADC之前,還需進行電平抬升,變為滿足ADC輸入電壓測量范圍要求的信號。其中,功出電壓信號經信號調理后還送至比較器電路,經過波形變換后由原來的正弦移頻信號變為3.3 V的方波信號,作為載頻信號的輸入源。比較器電路如圖3所示。電路由分壓電阻(R56,R59)、直流分壓電阻(R61,R62)、箝位二極管(V7,8V)、比較器N25A(LM393P)、上拉電阻R63及濾波電容等組成。本文引用地址:http://www.104case.com/article/173325.htm

5.3 主控單元

主控單元包括CPU及兩片CPLD。

CPU采用C8051F020單片機。由于F020內部集成有兩個ADC,所以在該系統中利用它的第18~25腳及29~34腳共14個端口作為多路模擬信號的輸入端口,由單片機完成所有模擬量的A/D轉換。在采集各路模擬信號的同時,F020還要從兩片CPLD讀取頻率、地址編碼及繼電器狀態數據,并對所有采樣數據進行實時計算處理,將所有轉換結果存入32 KB的外部存儲器。對于地址編碼信息,CPU只在每次上電后讀取1次,若有效,則保存,用作與微機監測通信的CAN節點地址,之后不再檢查地址編碼信息的變化。由F020的交叉開關優先權表可知,兩個UART的TX和RX可連到端口引腳。P0.O~P0.3,該系統中利用一組TX0和RX0接RS 232接口,另一組TXl和RXl接RS 485接口。

兩片CPLD均采用Altera公司的EPM3256ATCl44-lO芯片,數據采集及指示燈控制所需的控制時序及地址譯碼等電路均由CPLD產生。其中,CPLDl對48 MHz高精度一體化晶體振蕩器分頻,得到24 MHz及12 MHz同步時鐘信號,分別作為單片機及CAN控制器的系統時鐘。由于要采集的開關量路數較多,該系統將所有繼電器狀態輸入及五路地址編碼輸入均接至CPLDl,再由單片機通過數據總線從CPLDl分別進行讀取。CPLDl同時還生成兩路不同頻率的低頻測試脈沖,供生產調試時使用。CPLD2則負責完成所有低頻、載頻信息的采集。

5.4 與計算機通信接口

該系統提供RS 232或RS 485串行通信接口及CAN通信接口,其中串行通信接口主要用于生產調試,而現場應用中使用CAN總線與系統維護機交換數據。由于一條CAN總線上需掛接多個設備,該系統運用外部端子封線的方式為每個設備定義節點地址,地址編碼范圍為0~31。當節點地址為O時,CPU將工作于測試狀態,運行測試程序代碼,供設備調試時使用。

6 軟件設計

6.1 單片機程序設計

單片機程序固化在C38051F020單片機的內部FLASH存儲器中,在Cygnal IDE集成開發環境下,采用模塊化程序的設計方法,將軟件分為一個主程序和若干個子程序模塊,主程序流程見圖4。系統采用定時器O中斷方式,每0.1 ms分別對兩個ADC的某一通道采集一次,每通道連續采集512次,并將采集到的數據分別存入外部存儲器內的兩個連續緩沖區ADBufO和ADBufl中,再利用采集到的512個點的電壓瞬時值計算交流模擬輸入的電壓有效值。定時器0中斷模塊流程見圖5。

評論