基于PC104總線的429接口板

3 CPLD內部功能及實現

3.1 開發流程描述

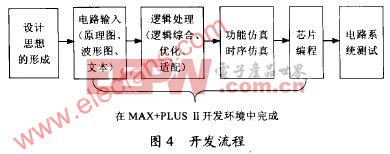

本系統中的CPLD使用Altera公司的MAX7000S系列可編程邏輯器件中的EPM7128SQC100-6型號,從最初的電路設計思想到MAX+PLUSII的波形仿真,再到CPLD芯片編程結束要經過的一般開發流程如圖4所示。

3.2 CPLD中的模塊設計

本設計中CPLD 的功能是實現ARINC429收發電路與接口板的接口總線PC104總線的數據通信。其功能模塊可以分為6部分,以下逐一介紹各模塊的功能及其實現的方法。

(1)產生AR1NC429控制器HS3282所需的TTCLK時鐘信號模塊

TTCLK即發射器時鐘信號,本設計中該信號有480 KHZ和1 MHZ兩種可選頻率,是由一個48 MHZ的晶振提供信號給CPLD,然后由CPLD編程產生480KHZ和1MHZ兩種信號以備選擇。該模塊用圖形編輯的方式實現。要產生3282所需要的480KHZ信號需要對輸入48MHZ信號進行兩次10分頻,要產生1 MHZ信號需要對輸入信號進行6分頻再8分頻。6分頻電路采用3個JK觸發器實現,8分頻電路采用74393實現,10分頻電路采用7490實現。

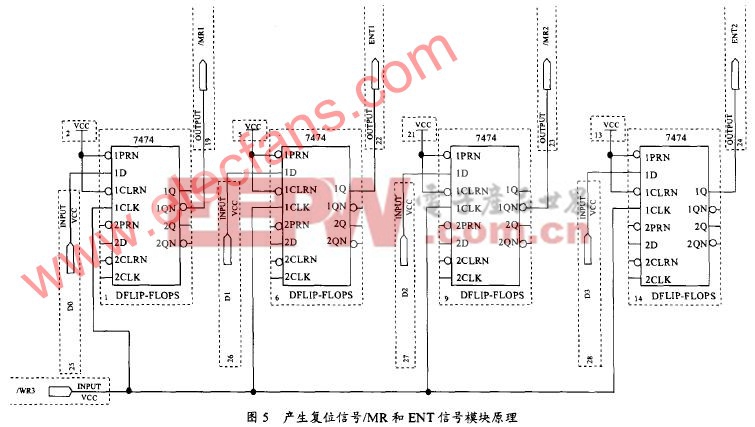

(2)產生復位信號/MR和控制發射器使能信號ENTX的信號ENT模塊

/MR是對3282的主復位信號,/MR將直接送到HS3282,而ENT將送到另一模塊中,用于控制發射器使能信號ENTX的產生,ENTX=ENT*/TXR,其中TXR為發送緩沖區空標志。該模塊也采用電路設計輸入方式。其電路主要由4個D型觸發器74LS74芯片來完成。輸入為總線驅動器的前4個輸出,即D0~D3,時鐘脈沖為產生HS3282讀寫信號模塊的一個輸出信號/WR3,輸出為兩個HS3282的復位信號/MR1和/MR2以及ENT1和ENT2。本模塊具體實現電路如圖5所示。

評論