基于單片機和可編程邏輯器件實現LED顯示屏

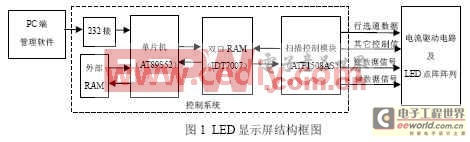

LED顯示屏主要由電流驅動電路及LED點陣陣列、控制系統和PC端管理軟件三部分構成(圖1)。控制系統負責接收、轉換和處理各種外部信號,并實現掃描控制,然后驅動LED點陣顯示需要的文字或圖案。控制系統作為LED顯示屏的核心部分,直接決定了顯示屏的顯示效果和性能的優劣。本文詳細分析采用Verilog HDL對ATF1508AS進行編程,實現雙口RAM訪問和產生LED點陣驅動電路所需的各種時序信號。

本文引用地址:http://www.104case.com/article/173025.htm1 LED顯示屏的基本結構及關鍵技術

本系統設計中,控制系統采用單片機+CPLD的方案來實現,整個控制系統可分為:信號接收及處理模塊和CPLD的掃描控制模塊和LED點陣驅動模塊,如圖1 所示。本系統的關鍵技術是使用雙口RAM和CPLD芯片,解決LED顯示屏中高速數據傳輸和快速掃描控制的難題,大大提高了動態顯示的刷新率。

信號接收與處理模塊的功能是AT89S52單片機通過串口接收PC送來的點陣信息,同時對點陣信息做各種不同的處理。利用雙口RAM IDT7007在單片機和ATF1508AS之間以共享的方式建立高速的數據交換通道。

CPLD的掃描控制模塊采用ATF1508AS芯片實現。其功能是從雙口RAM讀取點陣信息,串行化后送顯示掃描驅動電路,同時輸出各種所需的控制信號。CPLD具有掃描速度快,延時短等特點,克服了單片機由于傳輸速率慢而造成在大屏幕顯示時產生的閃爍效應。

2 基于CPLD的掃描控制模塊的設計

2.1 設計思想

本模塊的功能是從存儲器中讀取數據,將數據輸送到顯示屏體上,同時產生各種控制信號。時序產生模塊由兩部分構成,一是產生訪問雙口RAM的時序,二是產生LED顯示屏接口所需的各種信號。

硬件電路我們采用較常見的CPLD芯片ATF1508來實現控制系統中的時序產生部分。CPLD是一種具有豐富的可變成I/O引腳的可編程邏輯器件,不僅可以實現常規的邏輯器件功能,還可以實現復雜而獨特的時序邏輯功能。軟件我們采用Verilog HDL語言來進行設計。Verilog HDL是用于邏輯設計的硬件描述語言,已成為IEEE標準。利用Verilog HDL語言對ATF1508AS進行編程,實現掃描控制模塊所需的功能。

掃描控制部分的原理電路如圖2所示,ATF1508AS是核心部分,需要根據系統需要定義ATF1508AS的各個I/O端口,下面是I/O端口定義和內部寄存器定義的Verilog HDL語言代碼。

module LedSequ(color, datain, addrout, CE, OE, SEMR, RWC, sdr, sdb, sck, le, oe1, cs, clk, counter);

input clk; //系統時鐘

input[7:0] datain;//RAM數據輸入

input[1:0] color;//顏色控制

output[13:0] addrout;//地址輸出口

output SEMR,RWC;

output CE,OE,sdr,sdb,sck,le,oe1,cs;

output[3:0] counter;

reg[3:0] hcnt;//38譯碼器計數器

reg [7:0] data1;//數據寄存器

reg[3:0] counter;//38翻碼器輸出端

reg SEMR,RWC;

reg SDA,SDC;

評論