基于AT89S52單片機和ATF1508AS可編程邏輯器件實現LED顯示屏的硬件設計

本文引用地址:http://www.104case.com/article/173024.htm

2.3 LED顯示驅動時序信號的產生

CPLD 與LED點陣的驅動電路接口如圖 所示,其中:CS為3-8譯碼器片選信號;OE為BMI5026輸出使能信號,控制LED點陣是否能被點亮;LE為驅動芯片數據鎖存信號;sck為移位脈沖,將CPLD串行輸出的紅綠數據串行移入MBI5026(移位寄存器);A-D為雙3-8譯碼器構成的4-16譯碼器的數據輸入,實現顯示行選通控制; sdr為紅數據信號線;sdb為綠數據信號線。

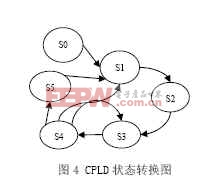

其工作過程為:S3狀態,sck脈沖置0,sdr和sdb分別輸出一位數據;S4狀態時,sck置 1,紅和綠數據分別移入相應移位寄存器BMI5026,若不足8位時,返回S3狀態,若不足一行時,返回S1狀態,讀下一個字節,若完成一行數據移位過程,則轉S5狀態;S5狀態時,置le為0,將BMI5026的緩沖寄存中一個顯示行的點陣數據送輸出寄存器,同時置cs1有效,控制第hcnt行的點陣顯示,然后判斷一屏內容是否顯示完成,返回s1狀態。圖4為完整的有限狀態機的狀態圖。

下面給出LED顯示屏體驅動時序信號對應的Verilog HDL程序代碼:

s3: begin

sck=1'b0;

sdr= SDA color[0];

sdb= SDC color[1];

OE=1'b1; CE=1'b1;

state=s4;

end

s4: begin // 移位輸出到LED顯示屏

sck = 1'b1;

shcnt = shcnt +1'b1;

if (shcnt = = 0)

begin

addr=addr+1'b1; //讀完一個字節地址記數器加1

byte=byte+8'b1;

if(byte= = nrow)// 如果讀完一行數據

begin

oe1=1'b1;//關LED顯示

cs=1'b1;

le=1'b0;//驅動芯片寫入數據

byte = 8'b0;

state=s5;//讀完一行數據則顯示

end

else state=s1;

end

else state=s3; //當前字節移位輸出

end

s5: begin

sck=1'b0;

le=1'b0;

counter=hcnt;

OE=1'b1;

CE=1'b0;

if(addr = = nscreen)

addr=0;

oe1=1'b0;

cs=1'b0;

state =s1;

end

led顯示器相關文章:led顯示器原理

評論