基于AVR單片機大容量數據采集系統的設計

MAX1304的12個I/O口中高8位分別與PB的8個口相連,低4位與PD的前4個口相連。其中可以通過配置高8位D0~D7來選通要啟動的模擬輸入通道。上電時,在啟動轉換位CONVST(接PA4)之前寫入配置寄存器,以選擇有效通道。寫配置寄存器時,將片選CS(接PA3)和寫使能WR(PA2)設為低電平,然后將D0~D7位裝載到并行總線,再將WR置為高電平,數據在WR的上升沿鎖存。轉換結束位EOLC(接PA0),所有選通通道轉換結束指示,在EOLC的下降沿,將CS(接PA3)和讀RD(接PA1)置為低電平,把第一個轉換結果置于并行總線。RD連續的低電平脈沖將轉換結果順次放到總線上。時序中最后一個轉換結果讀取后,額外的讀脈沖可以使指針重新指向第一個轉換結果。

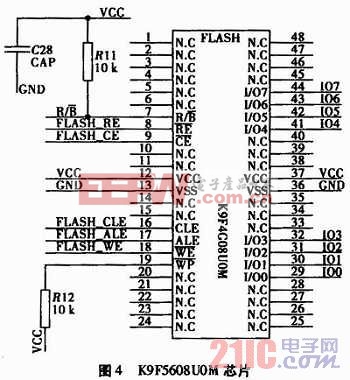

1.3 Flash芯片接口設計

K9F5608UOM 32M×8位閃速存儲器是sumsung公司生產的基于NAND技術的大容量、高可靠性存儲器。該芯片結構簡單,只有一顆存儲體;數據讀、寫、擦除速度快,按頁順序讀取平均每字節50 ns,與一般的SRAM相當;接口電路簡潔,8位雙向I/O口端口,地址,數據復用;編程簡單,片內的寫操作控制器自動執行所有的寫操作和擦除功能,包括提供必要的脈沖、內部校驗等,完全不用外部控制器考慮;數據完全性好,具有硬件寫保護功能,采用CMOS浮置門技術提高其壽命(可擦寫100,000次),數據保存10年不丟失。本設計中Flash的數據位與ATme-gal6L的C擴展口相連,控制位與ATmegal6L的B,D擴展口連接,實現數據的寫入操作。本文引用地址:http://www.104case.com/article/172739.htm

如圖4所示Flash芯片的8個I/O與ATmega16L的PC0~7相連,作為數據總線,用于輸入命令、地址、數據,在讀操作中輸出數據。忙閑指示(R/B)接PD4,器件運行狀態指示,當進行一個寫、擦、隨機讀取操作時,指示為低電平,操作結束后指示高電平。讀使能RE接PD5,控制把片內數據放到I/O中線上,在它的下降沿時數據有效,同時使內部的列地址自動加1。寫使能WE接PA5,用于控制把命令、地址和數據在它的上升沿寫入到I/O口,而在讀操作時必須保持高電平。片選CE接PD6,用于器件的選擇控制,在進行讀操作時,如果CE變為高電平,器件轉入待用狀態,而當器件寫操作或擦除過程中,則不受CE高的影響。命令鎖存使能CLE接PA7,使輸入的命令發送到命令寄存器,當變成高電平時,在WE上升沿命令通過I/O口鎖存到命令寄存器。地址鎖存器使能ALE接PA6,使輸入的地址發送到地址寄存器,當變成高電平時,地址在WE的上升沿被鎖存。寫保護WP提供由于芯片供電壓突變而引起的意外擦寫操作保護,當WP置低時,內部高壓源使芯片復位,引腳狀態不定,處于無操作態。由于本設計只需要向Flash中寫入數據,所以寫保護WP接VCC強制高電平。

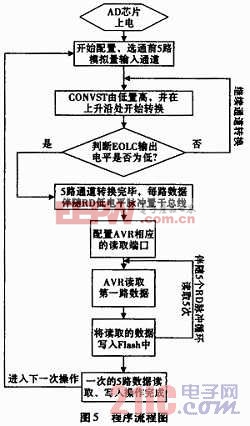

2 軟件設計流程

數據采集模塊負責數字化5個通道的模擬輸入量,將每路模擬量轉化為并行輸出的12位數字量。控制模塊的作用是將MAX1304所轉化的數據進行讀取并寫入到K9F4G08UOM存儲模塊中。

由圖5可以看到整個軟件的設計流程。MAX1304在上電時,開始配置寄存器選通前5路模擬通道輸入。在第一個CONVST脈沖上升沿時,5路并行采樣數據開始轉換。當所選通道數據全部轉化完畢時,EOLC將輸出低電平,可以通過查詢該端口狀態來了解轉換是否完成。當該端口電平為高時,繼續轉換下一路通道數據;為低時,ATmega16L配置相應的讀取端口為讀取狀態,將這一路數據讀到ATmega16L的緩存中,并控制Flash芯片將緩存中的數據寫入其中。隨著5個RD的脈沖信號,5路的數據將依次放置12位I/O總線上。所以,循環操作5次即可將一次并行采集的數據寫入Flash。然后進入下一時刻讀取寫入操作,整個過程循環操作即可。

3 結束語

通過這個5路采集電路,可以看出ATmega16L單片機和32M的K9F5608UOM大容量Flash存儲芯片在實際的接口設計是十分簡單的,而且操作靈活多變。在以上設計基礎上還可以將5路擴展到8路以內(通過配置MAX1304芯片可以實現),實現更多路的并行采集,并且可以根據實際情況來選擇大小合適的Flash芯片。這種可擴展的采集電路具有很高的性價比,無需選擇更昂貴的大容量控制芯片,可廣泛用于大批量數據采集記錄系統中。

評論