基于太陽能LED照明控制系統的處理器設計

3 指令集設計

在本系統中, 處理器要對AD 以及按鍵的輸入量進行處理。這些輸入數據位寬小且處理過程為常規運算,不需要進行使用高級數學算法進行繁雜的數據運算。所以本設計采用精簡指令集(RISC) 的設計方法。

精簡指令集具如下特點為: 指令系統的規模較小且復雜程度小; 操作數預存在寄存器中; 指令格式統一; 避免不必要的存儲器訪問。

采用RISC 指令集設計可直接減小芯片面積, 節省成本, 減少開發人員的開發與維護開銷。是嵌入式設備處理器的主流設計方法。

本處理器具有load/ store 結構, 也就是說與主存儲器通信只能通過LOAD 和STORE 指令進行。運算操作數只與寄存器組有關, 而并不在主存儲器上。TOP2的指令分為4 類: 運算指令、寄存器指令、跳轉指令、存儲器指令, 如表1 所示。

針對太陽能LED 照明控制系統的處理器指令集設計考慮到功耗及面積成本, 只包含6 條運算指令, 沒有連續移位指令和硬件乘法器。經測試本指令集可滿足上一節所述對處理器的功能需求。

作為RISC 體系的特點之一就是指令格式簡單規則, 筆者遵循這一原則, 指令集中的11 條指令均為4 位操作碼和12 位操作目標位 。

4 處理器結構

處理器主體結構如圖2 所示, 下面具體介紹處理器各部分。

4. 1 存儲結構

本處理器的存儲結構采用哈佛( Harvard) 結構。這是嵌入式處理器中被廣泛采用的結構, 如ARM、MIPS 等。特別適用于采用RISC 指令集的處理器。哈佛結構的主要特點是: 程序指令存儲通路與數據指令存儲通路物理上是分離的。使得兩個存儲器可以獨立編址、獨立訪問, 從而避免了程序訪問與數據訪問之間產生的相關性沖突。這中并行設計架構相當于提高了1 倍的吞吐量, 從而提高了處理器性能。

4. 2 流水線結構

基于哈佛存儲結構, 處理器核心的設計采用5 級流水線( pipe2line) 結構 分別是: 取指令級( IF) 、譯碼級( ID) 、寄存器訪問級( LO) 、運算級( EX) 、回寫級(WB) 。流水線的設計方法在高性能大規模系統中得到廣泛應用, 其實際上就是把規模較大、層次較多的組合邏輯分為幾個級, 在每一級插入寄存器并暫存中間數據。這樣做大大地增加了時鐘周期的利用率, 最大限度地發揮電路潛能。在不提高時鐘頻率的前提下提高了處理器效率, 可以實現在同等效率下相對于非流水線設計功率可降低25 倍 , 實現低功耗設計。

4. 3 片內其他模塊

整個芯片是圍繞著流水線核心實現。根據系統需求, 處理器要實現精確計時以及脈沖充電方式。為了實現這兩種功能, 在流水線核心的基礎上添加了兩個可獨立流水線運行的模塊: TIMER( 定時器) 和PWM( 脈寬調制) 。T IMER 模塊是16 位定時器, 時鐘源采用32 768 Hz晶振。其可以準確分辨1 s 時間單位, 誤差低, 可為本系統長年室外穩定工作提供支持。定時器可以供中斷和查詢2 種操作方式, 以供系統后期的靈活配置。PWM 是脈沖調制模塊。其功能是產生占空比可變的方波, 以驅動大功率MOS 管進行脈沖充電。其占空比變化范圍為0~ 100% , 步長1%。本模塊減輕了處理器流水線部分的負擔, 使脈沖驅動可與其他控制信號并行執行, 增強了系統的穩定性。

處理器片內還包含通用I/ O 控制單元。此單元完成對管腳數據方向的控制, 并為輸出數據提供保持功能, 對輸入數據進行同步。此單元對外部異步信號域與內部同步信號域進行隔離。避免產生信號毛刺, 簡化時序分析。

5 仿真與實現

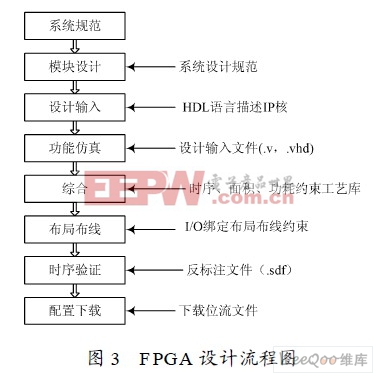

本設計通過FPGA 實現了所需求功能。設計流程如圖3 所示。

5. 1 仿真

在太陽能LED 照明控制系統中, 控制器所需要面對的指令流主要有三種: 運算指令流( 順序執行) 、分支跳轉指令流、循環指令流。

5. 1. 1 運算操作指令流( 加法)

完成加法指令需要的步驟包括:

( 1) 準備2 個操作數。這2 個操作數如果已經存在于寄存器組中則可以忽略此步驟, 如果其中一個或兩個是立即數或者在存儲器中, 則需要MOV 指令或LOAD 指令完成準備過程。

( 2) 進行運算。一條ALU 加操作。

( 3) 寫回存儲器。根據不同的需求會編譯出不同的指令組合, 這里以兩立即數相加結果存放在寄存器中為例進行加法操作。這需要首先執行兩條MOVD 指令準備操作數, 之后進行加法操作。需要注意的是, 在流水線中由于數據相關性問題, 在MOVD 指令之后ADD 指令不能馬上進入流水線執行。

評論