LED大屏幕控制電路設計方案研究

摘要:在綜合分析LED大屏幕顯示系統設計中控制電路的諸多設計方案的基礎上,分別給出了以單片機、可編程邏輯器件和嵌入式計算機技術為控制核心的不同設計方案的實現方法,對這幾種方案的特點進行了比較,并介紹了應用情況。

本文引用地址:http://www.104case.com/article/167981.htmLED點陣是公共信息的一種重要顯示終端,其中大屏幕LED點陣顯示屏在許多場合得以應用。大屏幕顯示技術比中小屏幕顯示難度更大,因為其屏幕大,LED點數多,而又要在極短時間內刷新每個點,這就要求其掃描速率必須非常高,此外,大屏幕作為信息發布的重要媒介,對其穩定性、可靠性以及可擴展性要求都很高,只有設計合理的控制電路才能滿足上述要求。本文著重討論LED大屏幕設計中控制電路的幾種設計方法,針對不同的設計要求給出了不同的解決方案。

1LED大屏幕系統的工作原理

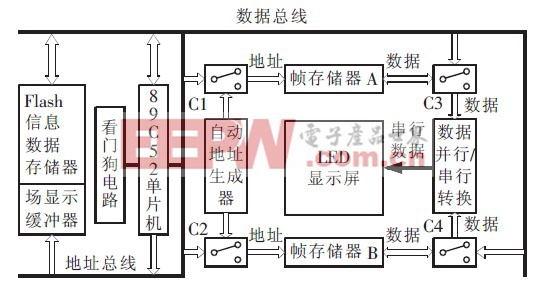

典型的LED大屏幕顯示系統主要由信號控制系統p掃描和驅動電路以及LED陣列組成,系統結構如圖1所示。目前大多數LED顯示屏的屏幕設計采用的是模塊化的結構,它的基本單元是LED顯示單元模塊,屏幕大小和形狀可靈活改變,顯示屏的安裝和維護也十分方便。

圖1系統原理框圖

信號控制系統是微機系統p單片機系統p微機Z單片機主從控制系統p可編程邏輯器件控制系統、紅外遙控系統p傳呼接收與控制系統等等。信號控制系統的任務是生成或接收LED顯示所需的數字信號,并控制整個LED顯示系統的各個部件按一定的分工和時序協調工作。行驅動電路多為三極管陣列,給LED提供大電流。列驅動由串入并出移位寄存器和鎖存器(或帶鎖存功能的移位寄存器)構成。

待顯示數據就緒后,控制系統首先將第一行數據送入移位寄存器并鎖存,然后由行掃描電路選通LED陣列的第一行,點亮一段時間后,再以同樣方法顯示后續行,直至完成一幀的顯示內容,如此循環往復。根據視覺暫留的原理,能夠實現24f/s的顯示才能夠讓肉眼沒有明顯的停頓感,相當于響應時間要達到,40ms以下。當LED顯示屏面積很大時,傳輸的數據量也非常大,從而增加了顯示系統的響應時間引起閃爍,為提高視覺效果,可以分區并行顯示。

在高速動態顯示時,LED的發光亮度與掃描周期內的發光時間成正比,所以通過調制LED的發光時間與掃描周期的比值(即占空比)可以實現灰度顯示。

2LED大屏幕控制電路的設計

控制電路的設計是大屏幕系統設計的核心,控制電路設計包括信號控制系統、掃描電路和驅動電路的設計,控制電路的設計一般由數據存儲器、數據緩存器、計數器p同步控制器p讀寫控制器p主從控制器、地址控制器、幀存儲器p數據選擇器、灰度調制器、移位寄存器等構成。目前來說,LED顯示屏控制電路設計廣泛采用兩類器件作為其控制核心來實現,一類是單片機控制系統,另一類是可編程邏輯器件。

2。1基于單片機的控制電路設計方案

基于單片機的控制電路主要有兩種方案,一種是一片單片機作為主控器件控制和協調大屏幕整個顯示系統的顯示,一種是多片單片機構成多處理器,其中一片作為主CPU,其它作為子CPU一起控制大屏幕的顯示。

圖2是采用單片CPU設計的控制電路機構示意圖,用89C52單片機作為控制核心。單片機接收從PC機或其他信息源發送來的顯示數據,存儲在Flash中,同時用RAM6264作為場顯示緩存區,以實現不同顯示播出方式。89C52控制切換開關C1,C3和C2,C4同時對幀存儲器A,B交替進行數據的讀寫操作,將讀出的數據進行并行5串行轉換送給顯示屏進行顯示刷新。其中,自動地址生成器由4個計數器串聯構成,并配以振蕩電路提供計數時鐘,對于一個M×N個像素的單色屏,當刷新頻率為60Hz時,計數頻率為M×N×60Hz對于多灰度級彩色大屏幕,數據送到顯示屏之前要進行灰度調制重現圖像的色彩,對數據的處理速度要求更高,采用單片機控制可能在速度上無法滿足要求。

圖2單片CPU控制電路結構示意圖

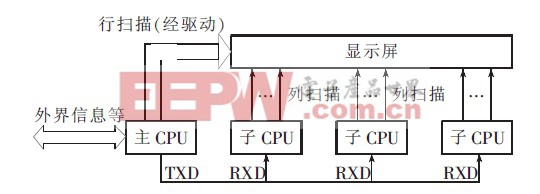

由于目前很多單片機的I/O口具備了15mA以上的驅動能力且價格比較便宜,因此在大屏幕的設計中也采用多處理器方案。系統的基本特點是:一個顯示組中有多個處理器,包括一個主CPU和多個子CPU,其結構示意圖如圖3所示。主CPU的任務是通過數據采集或與外界通信等獲取顯示信息,再傳輸給子CPU,主CPU還負責行掃描和發送顯示同步信息等。子CPU接收主CPU的數據信息并存放到內部RAM。中,再根據主CPU發出的控制信息選擇適當的列輸出口進行列掃描。假設每個子CPU可用作輸出口的最多引腳數為m,而每塊LED矩陣的列數為n,則每塊芯片所能驅動的LED塊最大數為m/n這樣,每個單片機負責一塊或幾塊>LED塊,靈活性強,便于擴展,同時減輕了主CPU的負擔,提高了點陣的刷新頻率。

圖3多CPU控制電路結構示意圖

在多畫面顯示的大屏幕設計中,這種方案較為理想,對不同的顯示畫面采用單獨的子CPU進行列掃描,再通過主CPU進行統一的行掃描,雖然控制電路使用的元件較多,但電路結構簡單,易于實現。

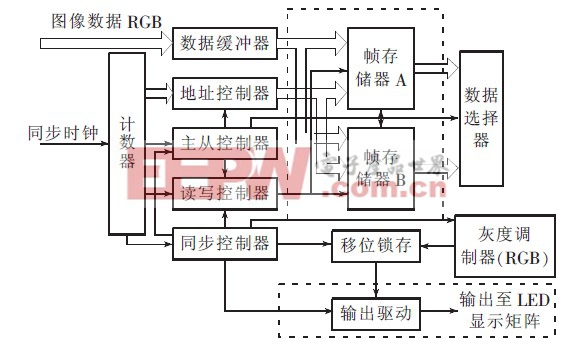

2。2基于CPLD/FPGA的控制電路設計方案

頻圖像信號頻率高:數據量大,要求實時處理,加之LED大屏幕電路的數字邏輯相當復雜,采用CPLD/FPGA設計控制電路,可以簡化系統結構,便于調試。圖4是CPLD/FPGA設計控制電路的原理圖。采用CPLD/FPGA器件對其中的同步控制、主從控制、讀寫控制和灰度調制等大量電路進行了集成,使圖像數據處理更為快速,圖像更加穩定,而且系統結構緊湊,工作可靠性有所提高。

圖4CPLD/FPGA控制電路原理圖

圖4中虛線以外的其它功能模塊均有CPLD/FPGA編程實現,將復雜的硬件電路設計通過軟件編程來取代。與圖2的單片機控制電路對比來看,電路結構明顯更簡潔,電路的面積減小及可靠性增強,調試也更為簡單,由于CPLD/FPGA可以并行處理多個進程,比起單片機對任務的順序處理效率更高,點陣的刷新頻率也隨之提高。

評論