基于MPEG-4視頻標準數字視頻錄像機的設計及實現

攝像頭采集輸出信號為NTSC,PAL或SECAM制式的電視信號,必須經過視頻解碼處理才能轉化成適合AT2042進行編碼的數字信號。TVP5150是TI公司生產的一款電視信號解碼專用芯片,它對輸入的模擬信號進行A/D轉化,通過設置相應的寄存器可以使輸出信號滿足RGB格式或YUV422格式。由于在本系統中AT2042視頻接口滿足ITU.RBT656標準,故TVP5150輸出配置為8位YUV422格式。如圖4所示。

現在的數字電視視頻接口還沒有實現統一的工業標準,故在視頻輸出端設計時,仍使用現在比較流行的A/V接口或S-video接口。由于上述2種接口傳輸的為模擬電視信號,故在AT2042的視頻輸出端口需要增加一級處理,即將數字信號轉化為模擬電視信號。在后端設計中選用SAA7121,它是一款專用的電視信號編碼芯片,可以將輸入的數字信號經過內部的D/A轉化為適于傳輸的模擬電視信號,通過配置相應的寄存器可以輸出滿足S-video接口或復用接口的信號。

1.3 AT2042的主機接口

主控CPU(S3C2410)和AT2042是數字視頻錄像機的核心處理芯片,S3C2410控制整個數字視頻錄像機系統的運行,AT2042除完成對視頻信號的硬件壓縮編碼外,還可對壓縮后的視頻數據進行硬件解壓縮。AT2042壓縮編碼后的視頻數據通過芯片內部集成的Mux FIFO接口輸出后,外部主CPU負責對其進行USB存儲器處理,處理后的視頻數據可以存儲在物理介質上,以便在需要時通過鍵盤操作進行回放。

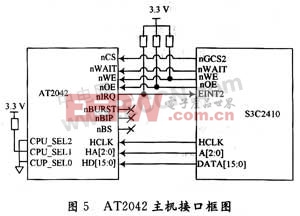

圖5為S3C2410與AT2042接口框圖。

AT2042的CPU_SEL[2:0]是主控CPU選擇引腳,經配置這幾個引腳的高低電平,使AT2042可選擇主控CPU,CPU_SEL[2:0]為010選擇ARM結構芯片;

nCS,nWAIT等為總線控制信號線;

HCLK是AT2042主機接口的工作時鐘,一般要求工作在50 MHz,當S3C2410在復位后設置FCLK為200MHz,HCLK為100 MHz,PCLK為50 MHz。故將S3C2410的PCLK引腳與AT2042的HCLK引腳相連。

通過這種機制,S3C2410可以實現簡單的訪問AT2042。

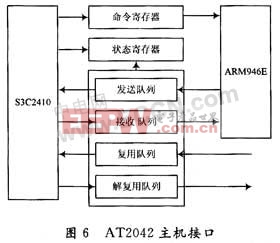

AT2042與CPU的通信機制如圖6所示,CPU對AT2042的控制和訪問主要通過AT2042的2個寄存器(status register和command register)和4個FIFO(Tx FIFO,Rx FIFO,Multiplex FIFO和De-Multiplex FIFO)完成。

評論