基于SSI208接口模塊的光電 編碼器數(shù)據(jù)采集設(shè)計(jì)

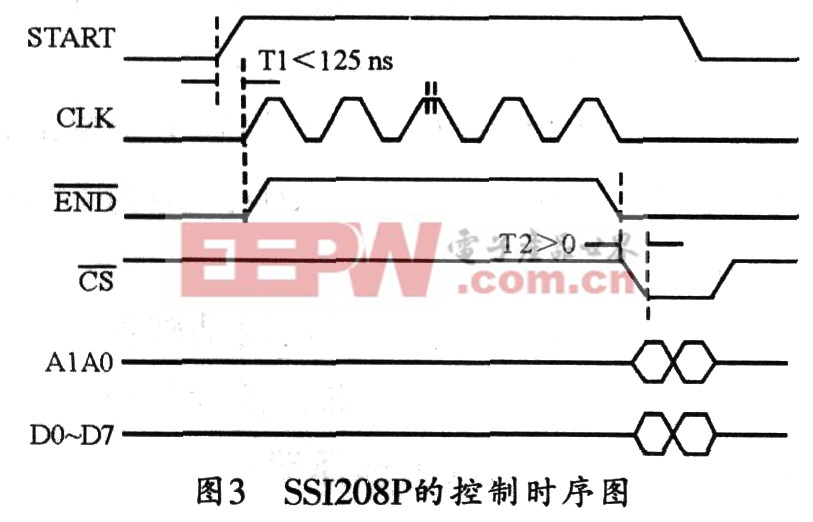

1.3 SSI208P控制時(shí)序

SSI208P的控制時(shí)序如圖3所示。一般可在START上升沿啟動(dòng)一次SSI編碼器數(shù)據(jù)收發(fā)過(guò)程。START電平升高后的125ns內(nèi),SSI208P模塊開(kāi)始向編碼器發(fā)送一幀同步時(shí)鐘脈沖信號(hào),脈沖的個(gè)數(shù)由編碼器的精度決定,同時(shí)轉(zhuǎn)換結(jié)束管腳END變高。發(fā)送脈沖期間,管腳END保持高電平,轉(zhuǎn)換結(jié)束,END管腳電平變低后,即可從DO~D7并行讀取編碼器數(shù)據(jù),每次讀取八位,并由Al、AO控制輸出數(shù)據(jù)的高低位,00表示讀取最低八位、11表示讀取最高八位。如對(duì)16位編碼器,只需讀取兩次(A1、AO分別為00、01),最多可以讀取32位數(shù)據(jù)。編碼器并行數(shù)據(jù)讀取結(jié)束后,應(yīng)將START管腳置低,以準(zhǔn)備啟動(dòng)下一次轉(zhuǎn)換。本文引用地址:http://www.104case.com/article/166836.htm

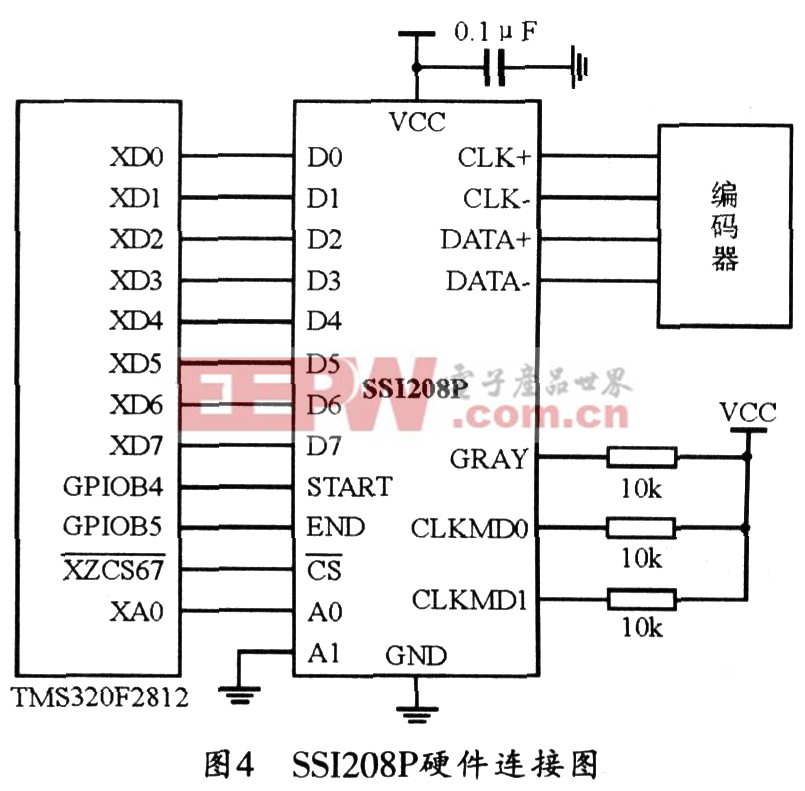

1.4 基于SSI208P的接口設(shè)計(jì)

采用SSI208P模塊可以大大簡(jiǎn)化單片機(jī)、DSP、PCI04等控制器擴(kuò)展SSI編碼器接口的軟硬件設(shè)計(jì)。下面給出一種基于DSP處理器TMS320F2812的典型應(yīng)用。圖4所示為DSP處理器TMS320F2812與SSI208P模塊的硬件連接原理圖。本編碼器為單圈16位絕對(duì)式角度編碼器,編碼器輸出數(shù)據(jù)格式為格雷碼,SSI208P模塊的八位數(shù)據(jù)總線與TMS320F2812的低八位數(shù)據(jù)線相連。由于使用的編碼器為16位,所以僅需一位地址線即可區(qū)分編碼器數(shù)據(jù)的高八位和低八位,可使用外部地址片選管腳/XZCS67作為SSI208P的外部片選信號(hào),并使用通用IO口GPIOB4控制SSI208P模塊啟動(dòng),同時(shí)使用通用IO口GPIOB5進(jìn)行SSI208P模塊轉(zhuǎn)換結(jié)束狀態(tài)查詢。設(shè)計(jì)時(shí)應(yīng)在CLKMDO、CLKMDl接上拉電阻,并將SSI208P模塊同步時(shí)鐘頻率配置為2MHz。將GRAY管腳拉高,SSI208P模塊即可將編碼器輸出的格雷碼數(shù)據(jù)轉(zhuǎn)換成BCD碼。

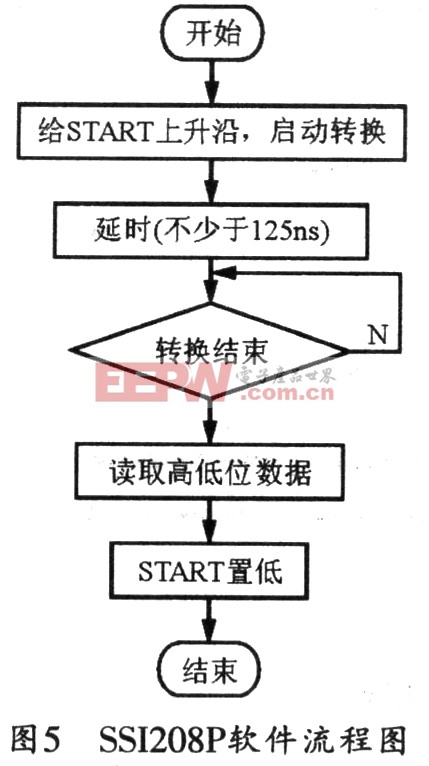

由SSI208P模塊的控制時(shí)序圖可以看出,SSI208P模塊的啟動(dòng)轉(zhuǎn)換控制和數(shù)據(jù)讀取操作比較簡(jiǎn)單,其軟件流程如圖5所示。

評(píng)論