基于TMS320VC550的JPEG視頻壓縮系統的實現

1 引言

本文引用地址:http://www.104case.com/article/166768.htm隨著網絡和多媒體技術的發展,視覺通信的重要性和需求急劇增加,如桌面視頻會議、移動終端、基于因特網的視頻通信等。這些視覺信息內涵豐富,但數據量大,必須壓縮數據。但采用多種方法壓縮圖像數據,其數據量仍然巨大,這就對計算機處理速度、傳輸介質、傳輸方法和存儲介質提出較高要求。因此,數據壓縮作為數據圖像處理的關鍵技術之一,對研究圖像壓縮編碼技術具有重要價值。

嵌入式微處理器中,DSP具有靈活、高速、便于嵌入式應用等優點,特別適合復雜算法處理的應用。數字視頻圖像壓縮系統利用DSP作為其嵌入式平臺,充分發揮其性能優勢,較好地提高編碼效率,滿足圖像實時處理需要。因此,這里介紹一種基于TMS320VC5509A型DSP的視頻壓縮系統。

2 靜止圖像的壓縮編碼標準JPEG

JPEG(Joint Photographic Experts Group)是由國際標準化組織(ISO)提出面向靜止圖像編碼的標準,其處理方法依次使用離散余弦變換、量化、Z行掃描、游程編碼和不變字長編碼。JPEG算法定義了以下4種運行模式:

(1)基于DCT順序型模式按照從左到右、從上到下的順序對圖像進行掃描和編碼,稱為基本系統。

(2)基于DCT遞增模式 按照從粗到細的順序對一幅圖像進行編碼,適用于傳輸時間長、用戶喜歡圖像從粗糙到清晰的場合。

(3)無失真編碼模式保證重建圖像與原始圖像完全相同。

(4)分層編碼 采用各種分辨率對圖像進行編碼。

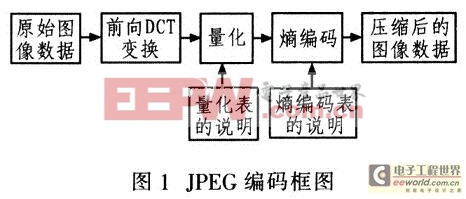

該系統采用基本系統模式。圖1是JPEG的編碼框圖。

3 硬件系統設計

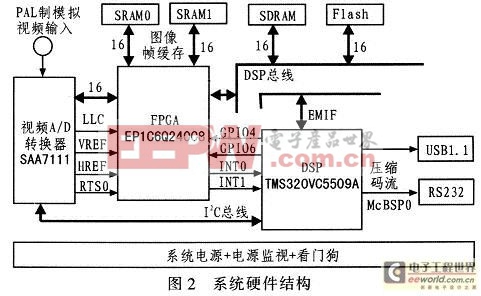

該視頻壓縮系統直接與PAL制攝像頭的輸出端相連,來采集、預處理和壓縮現場圖像,再以USB或RS232方式將處理后的圖像數據傳給上位機。圖2為視頻壓縮系統硬件結構圖。

該系統硬件設計以TI公司的TMS320VC5509A型數字信號處理器為核心,包括視頻采集電路、FPGA預處理電路、存儲器擴展、系統電源和看門狗電路等。系統中TMS320VC5509A為中央處理器;SDRAM為DSP外擴數據存儲器;Flash為程序存儲器,用于系統上電自舉;模擬攝像頭與視頻 A/D轉換器負責視頻圖像采集;FPGA用于地址譯碼、隔行運算,控制兩片SRAM用于緩存視頻A/D轉換器轉換后的數字圖像。從系統設計成本考慮,這里選用Altera公司的可編程邏輯器件EPIC6Q240C8型FPGA。該器件是Cyclone系列器件中一款非BGA封裝的可用I/O引腳最多的 FPGA。

評論