基于WM8741的音頻解碼器設計

3 解碼器硬件設計

3.1 硬件組成

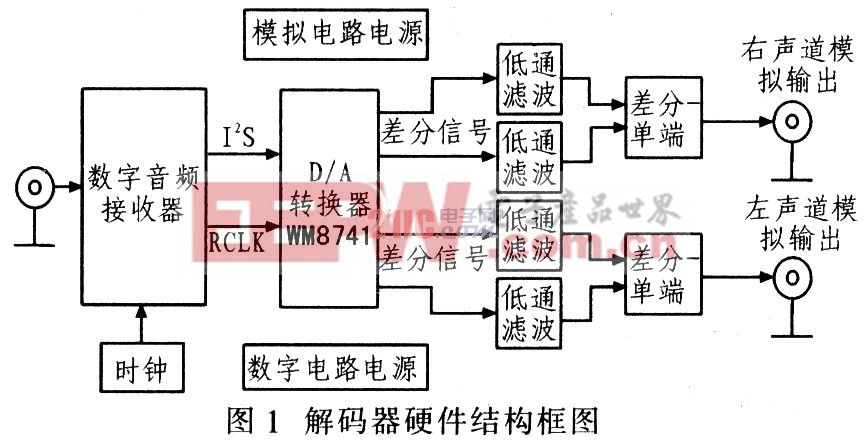

圖1是該解碼器硬件結構框圖,其中數字音頻接收器采用Cirrus Logic公司的高速數字音頻接收器CS8416,該器件支持包括S/PDIF在內的多種音頻輸入,取樣頻率范圍為32~192 kHz。CS8416通過I2S接口與WM8741相連接。I2S總線只處理音頻數據,其他控制信號必須單獨傳輸。CS8416的工作原理:接收器把接收到的S/PDIF格式的數字音頻數據進行解碼轉換,同時重建音頻數據中的時鐘并提供給后續WM8741,音頻數據則通過I2S總線接口發送給WM8741。WM8741按照設定的參數完成數模轉換后,再以差分形式輸出左右通道的模擬音頻信號,并經低通濾波器濾除高頻諧波噪聲,最終得到高質量模擬電壓信號。如果輸出接口為RCA,還需將差分信號轉換為單端信號。

3.2 數字音頻信號接收模塊

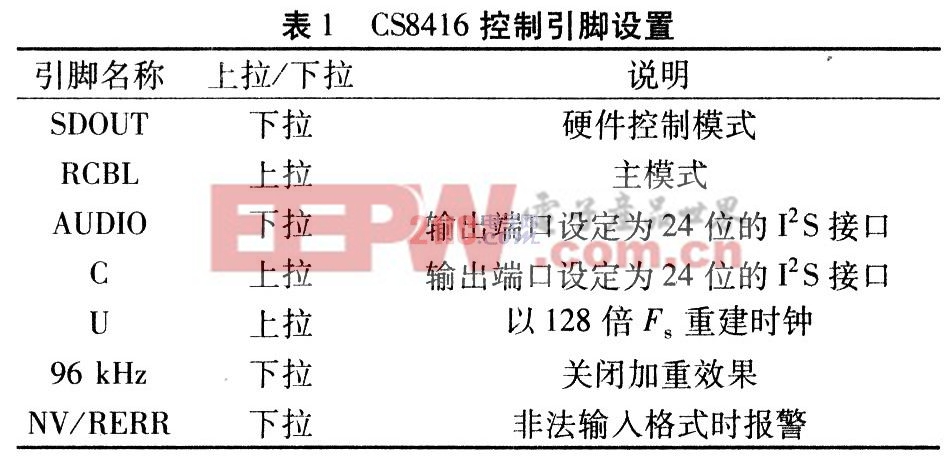

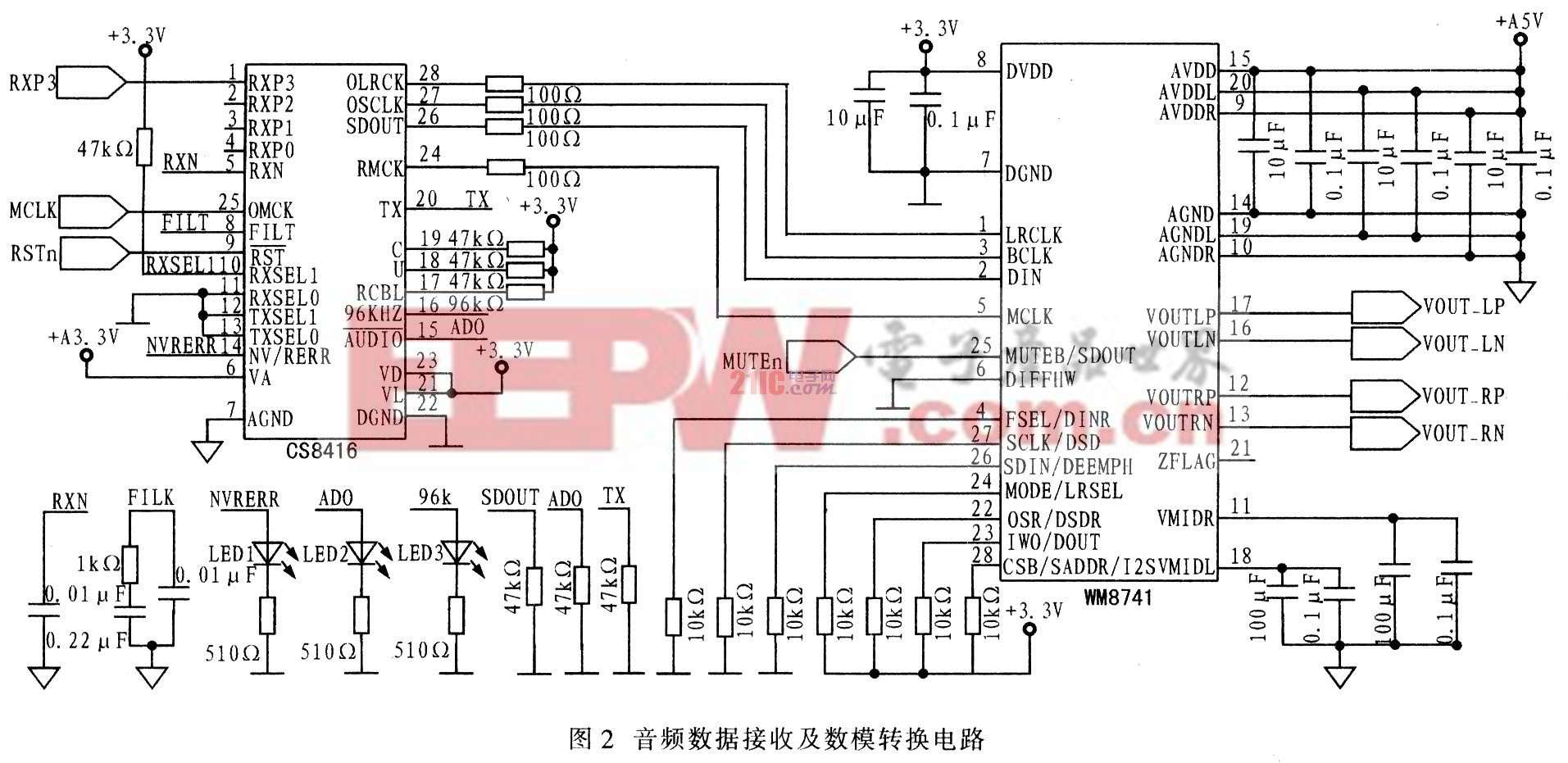

CS8416是數字音頻信號接收電路的核心。在軟件控制方式下,MCU通過SPI或I2C接口沒置參數。該方式還可靈活更改內部配置。在無MCU時則通過硬件控制方式改變其特定引腳電平實現控制。由于本系統中無MCU,因此采用硬件控制方式。在SDOUT引腳上用一只47 kΩ電阻下拉至地即可,且引腳AUDIO、RCBL、U、C等不能懸空,必須通過一只47 kΩ電阻上拉至高電平或下拉至低電平,以便系統復位后,CS8416通過檢測這些引腳電平決定其工作狀態。表1為該系統設計的控制引腳的配置。

CS8416具有多個可選的音頻輸入接口。該系統設計是將CS8416的引腳RXSEL1接高電平,引腳RXSEL0接地,選擇引腳RXP3作為音頻數據輸入接口。音頻時鐘重建通過片上的鎖相環(PLL)實現,該鎖相環不需要過多地改變外部元件即可在很大范圍內鎖定輸入音頻數據中的取樣頻率Fs。但外接電阻電容組成的濾波電路也會影響其頻率變化范圍。為了獲得一個低抖動的重建時鐘,外接濾波器的電阻電容值如圖2所示。

評論