JPEG圖像硬件解碼低功耗設計

IDCT設計中使用了零值判斷邏輯電路、門控時鐘、并行流水線等技術,使得整個電路在滿足處理速度和精度要求的基礎上大大降低了功耗。

3.1 零值判斷邏輯電路

在整個圖像解碼過程中,每8×8個數據塊中有約90%的數據的DCT系數為零,對這些零值進行IDCT變換并無意義。因此,本設計添加了零值判斷邏輯來消除不必要的乘法運算。零值判斷邏輯電路由8×8累加器陣列、零值判斷邏輯模塊和復選器MUX構成。通過零值邏輯模塊判斷,當操作數不全為零時,使能信號變成高電平,將操作數取到寄存器中,然后再進行乘法運算。如果操作數全為零,則封鎖累加陣列,直接通過MUX輸出0。零值判斷邏輯能有效地降低功耗,且電路簡單,面積與延遲時間幾乎可以忽略不計。

3.2 基于鎖存器的門控時鐘

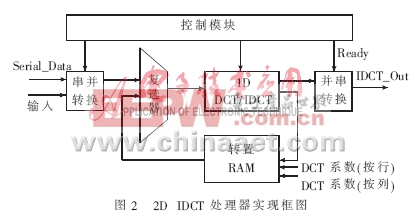

通過控制電路的輸入時鐘可以使得一部分電路降低工作頻率或者停止工作,從而降低整個電路的功耗。2D DCT/IDCT的電路主要由3部分組成:1D DCT/IDCT單元、轉置存儲器、輸入輸出處理單元。

轉置存儲器部分只有在每次1D DCT/IDCT處理的最后才進行更新,而輸入輸出處理單元只有在數據輸入輸出的時候才工作。因此,控制這幾部分電路的輸入時鐘,使其在大多數時間停止工作即可以有效地降低功耗。設計結果表明,在面積僅增加2%的情況下系統功耗可降低13%。

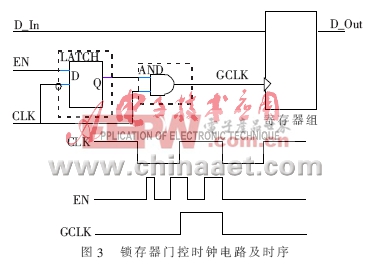

基于鎖存器的門控時鐘可以實現上述功能,它具有不需要數據選擇器、面積較小、可以減小時鐘網絡上電容、減少門控寄存器的內部功耗等優點。鎖存器門控時鐘電路及時序如圖3所示。

3.3 并行流水線

本設計使用加法和移位運算代替IDCT快速算法中的浮點乘法運算單元,用高度并行流水線VLSI結構加快數據處理速度,其處理數據的時間不到串行結構的1/5。因此,時鐘頻率可以相應地降低到串行結構的1/5左右,從而降低系統的功耗。例如,使用2個16×8的乘法器同時并行計算高位部分和低位部分,分別得到高位部分積和低位部分積,然后進行移位相加。實現電路運算時實現時間重疊、資源重復使用和資源共享,提高了系統的并行性,以此提高了乘法電路的運行速度和效率。

4 仿真和綜合結果

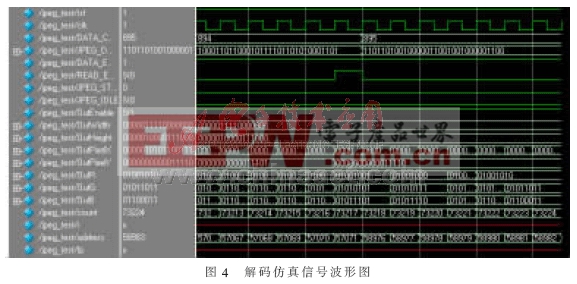

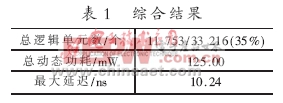

本文選用1幅1 920×1 080大小的JPEG圖像,Modelsim進行RTL級仿真后的波形如圖4所示。圖中JPEG_DATA是碼流數據,OutR、OutG、OutB是解碼仿真結果[4]。在100 MHz的頻率下對解碼核心模塊進行綜合[5],結果如表1所示。

本文有別于以往用軟件實現JPEG解碼,而是在用硬件實現JPEG解碼的同時,改進硬件結構,通過多種易于操作的方法來降低硬件解碼能耗。通過EDA工具驗證,完全可以滿足JPEG圖像硬件解碼的要求。

評論