音頻交換混合矩陣設計與實現

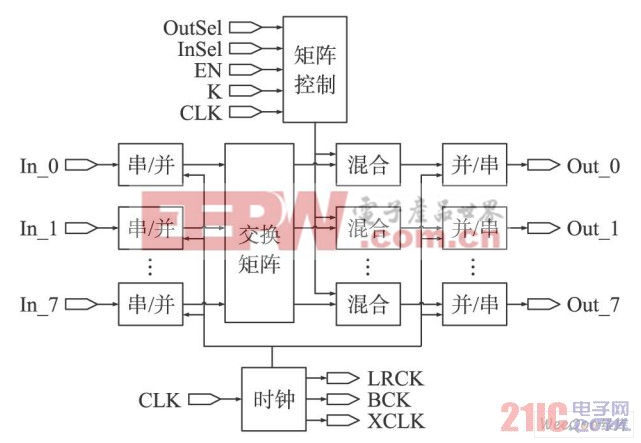

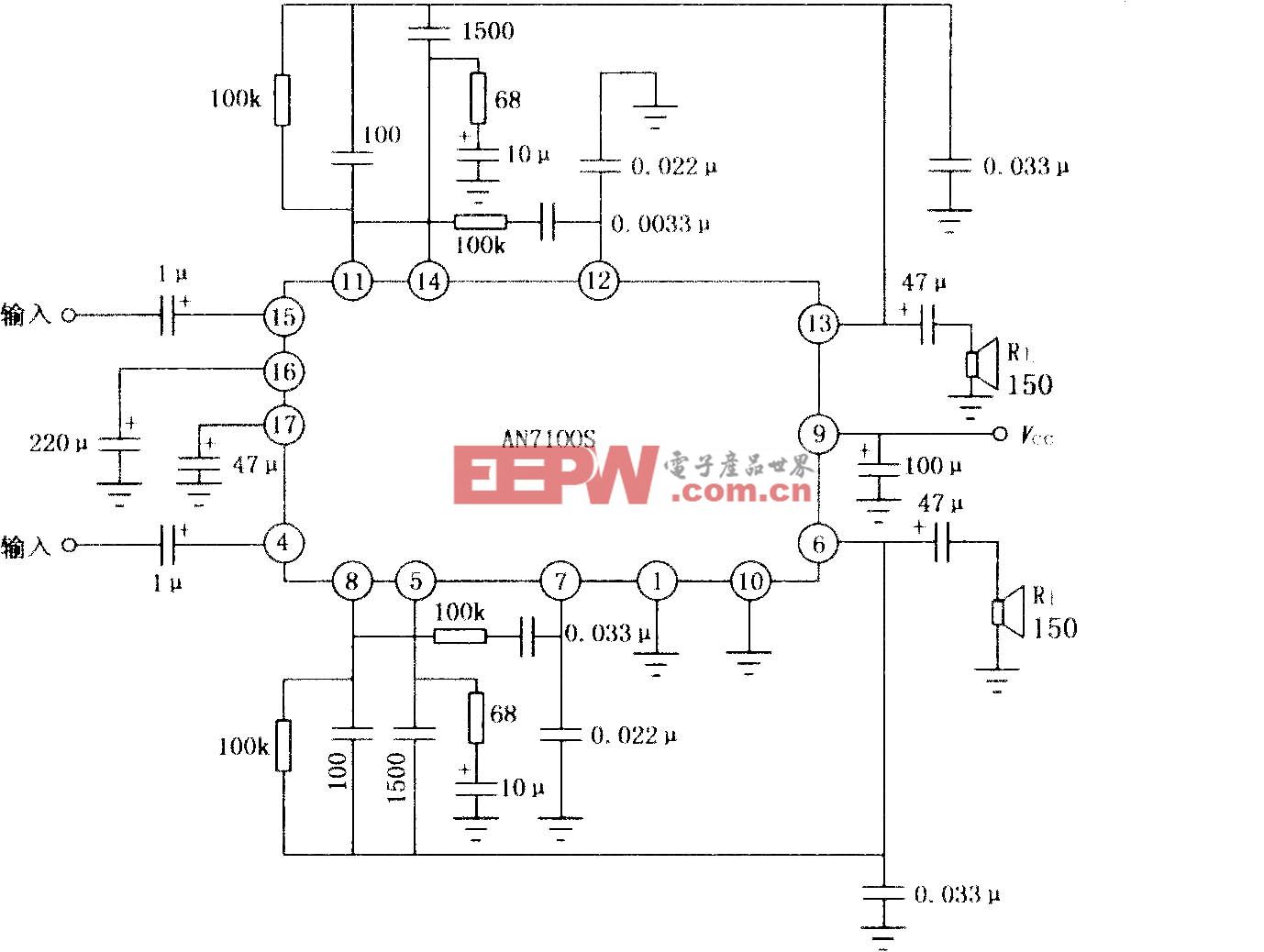

2. 3 FPGA及其程序設計

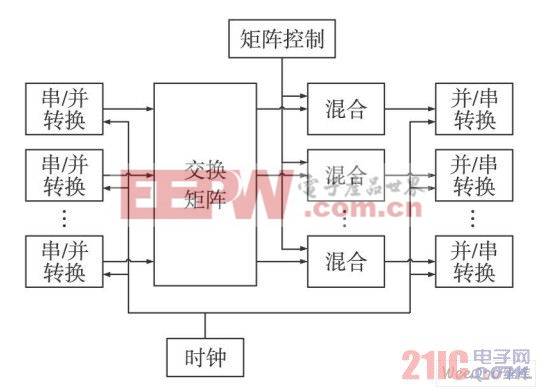

FPGA內部包含串/并轉換、交換矩陣、混合、并/串轉換、時鐘模塊和矩陣控制模塊,其內部模塊框圖如圖4 所示。FPGA 選用Altera的EP2C35 芯片,其具體參數見文獻。

2. 3. 1 時鐘模塊

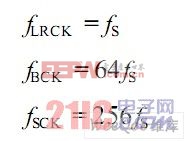

時鐘模塊的功能是為串/并、并/串轉換模塊提供統一的全局時鐘。系統需要的時鐘信號有三種,分別是:系統時鐘( SCK) 、位時鐘(BCK)和聲道時鐘(LRCK) ,各時鐘頻率由采樣頻率( fS )決定:

圖4 FPGA內部模塊框圖。

本系統中,采樣頻率fS 為97. 7 kHz,通過一個50MHz的外部時鐘信號分頻產生上述各個時鐘。

在模塊內建立一個9 bit累加計數器Q,在時鐘信號的上升沿完成一個遞增計數, 當數值計到滿值111111111時, 在下一個時鐘周期將Q 置0。將XCLK、BCK、LRCK輸出分別連接到計數輸出的第0、第2和第8位,并將第3 - 第7位合并成另一個計數輸出S_Count,用于控制串- 并和并- 串轉換的位計數。所以,實際生成的fSCK為25 MHz, fBCK為6. 25MHz, fLRCK和fS 為97. 7 kHz。

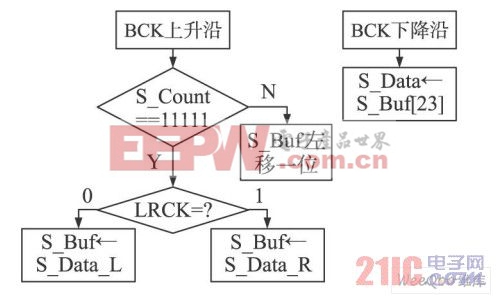

2. 3. 2 輸入串/并轉換模塊

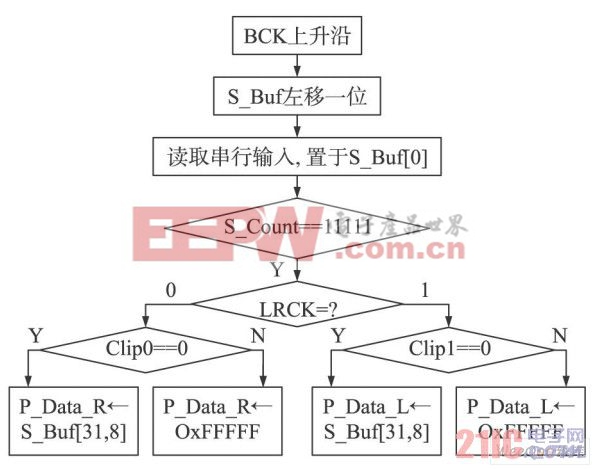

該模塊負責將PCM4204輸入的串行PCM編碼轉換為并行數據,送入交換矩陣模塊進行處理。模塊內部建立通過一個32 bit移位寄存器( S_Buf) ,用來存儲串行數據,根據聲道時鐘(LRCK)的動作來控制并行輸出。串/并轉換流程如圖5所示。

圖5 串/并轉換流程圖。

2. 3. 3 矩陣控制模塊

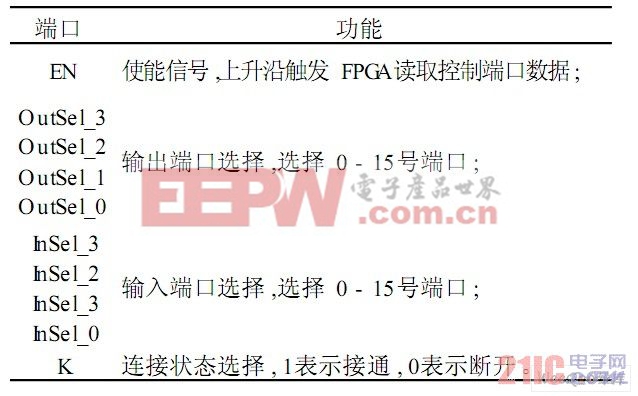

該模塊的功能為:接收外部控制單元的命令,控制矩陣實現轉接操作。FPGA保留10個GP IO作為使能控制端口,定義為表1。

表1 矩陣控制端口定義

模塊的輸出是16組16 bit并行數據,形成一個矩陣表。其中,每組數據代表輸出端口,該組中的每個bit代表對應的輸入端口,表中的元素代表相應的輸入與輸出之間的連接關系, 0表示斷開, 1表示連接。

使用時,先選擇需要進行操作的輸入和輸出端口以及操作狀態,然后向EN輸入高電平,觸發控制電路進行工作,將選擇的輸入與輸出信號相連接或斷開。

2. 3. 4 混合模塊

該模塊由數據緩沖寄存器(AdderBuf)和加法器(Adder)兩部分組成。數據緩沖寄存器讀取控制端口( Sel)的狀態,然后判斷各個輸入是否有效,即是否送入到輸出端口。若某輸入端口有效,則將該端口數據直接送入加法器;若無效則送出數據0。

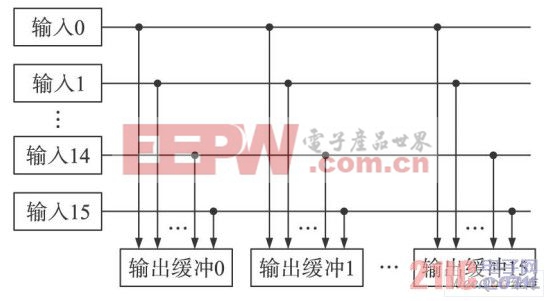

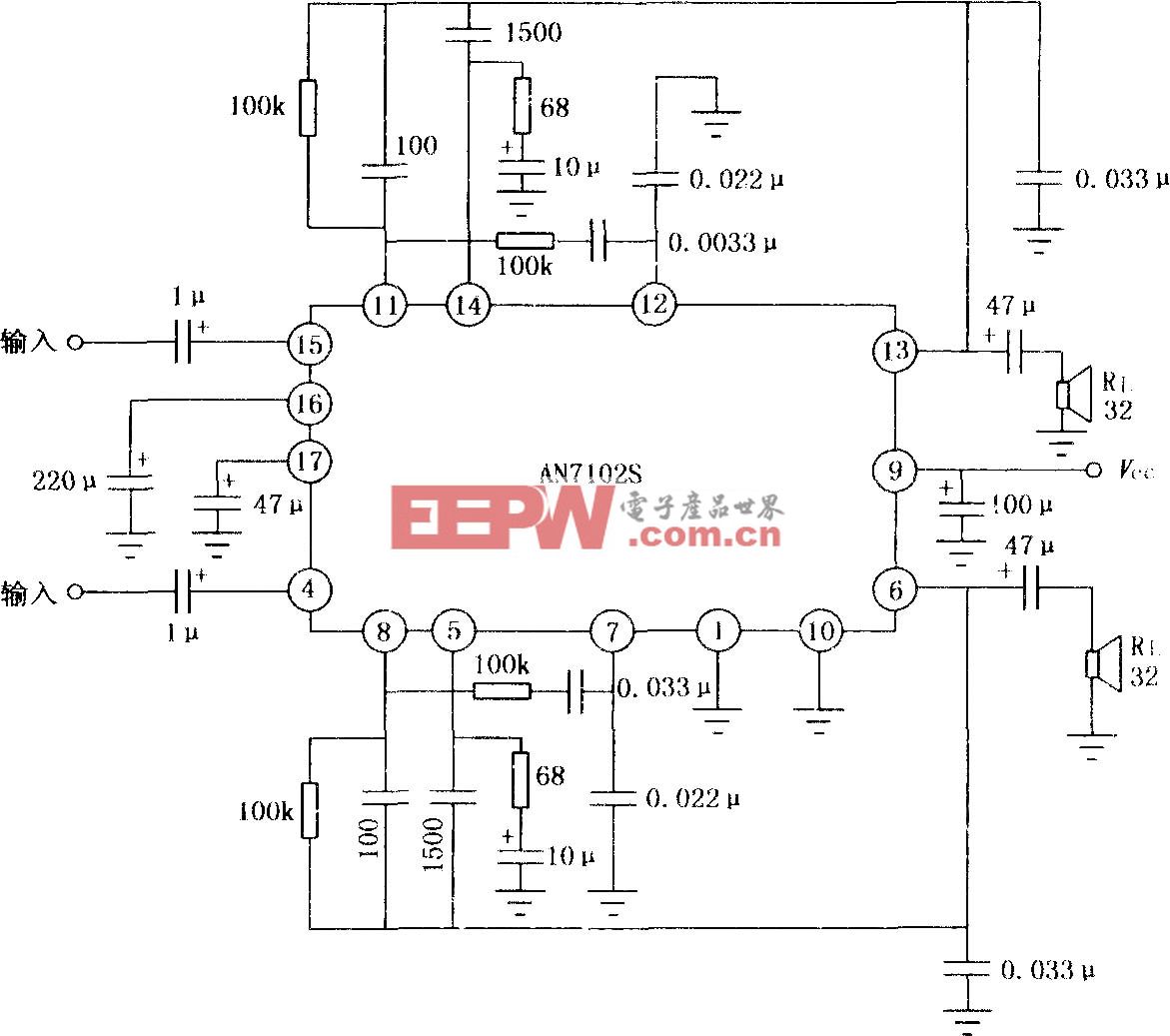

2. 3. 5 交換矩陣模塊

交換矩陣的工作原理是一個16轉256的分配器,將每一路輸入分配為16路,分別送入每一路輸出的混合模塊中。其結構如圖6所示。

圖6 交換矩陣模塊結構圖。

2. 3. 6 輸出并/串轉換模塊

該模塊負責將混合模塊輸出的24 bit并并行數據轉化為PCM1681能夠接收的串行PCM編碼。數據傳輸格式與PCM4204相同。模塊內部建立一個24 bit移位寄存器,用來產生串行輸出,根據聲道時鐘(LRCK)的動作判斷讀取并行輸入。并/串轉換流程如圖7所示。

圖7 并/串轉換流程圖。

3 系統仿真及實現

3. 1 系統仿真

FPGA總體端口及模塊框圖如圖8所示。

圖8 FPGA總體端口及模塊框圖。

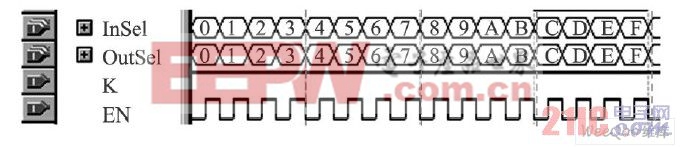

由時鐘輸入端(CLK)輸入50 MHz時鐘信號;在交換控制端口送入控制信號,使In_0與Out_0相連, In_1與Out_1相連, ……, In_7與Out_7相連,控制信號輸入如圖9所示。

圖9 控制信號輸入。

評論