基于計數器的數字電子鐘的設計

2 單元電路的設計

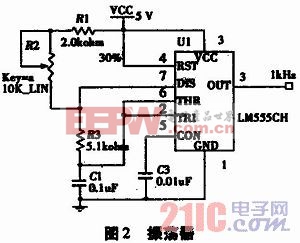

振蕩器是數字電子鐘的核心,振蕩器的穩定度及頻率的準確度決定了數字電子鐘的準確程度。通常選用晶振來構成振蕩器電路。本文采用555構成的多諧振蕩器。它是一種無穩態電路,在接通電源后,不需要外加觸發信號,電路狀態能夠自動地不斷變換,產生矩形波的輸出。該電路存在兩個暫穩態。電容C1在(1/3)VCC和(2/3)VCC之間充電和放電。第一個暫態是:當電源剛接通時,電源電壓通過R1、R2對C1充電,充電時間為T1=(R1+R2)*C1;第二個暫態為是,電容C1通過電阻R2和放電管放電,放電時間為T2=R2*C1。所以該電路的振蕩周期為T=0.7(R1+2*R2)*C1,頻率F=1/T。我們可以通過改變R1、R2和C1的值得到所需的頻率。該電路如圖2所示。本文引用地址:http://www.104case.com/article/166053.htm

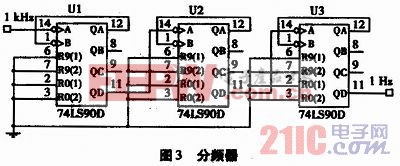

數字電子鐘的時基信號是1 Hz,由555定時器產生的1 kHz的信號必須經過分頻器才能獲得1Hz的信號。分頻器實際也是計數器,本設計中所用的分菝器有兩個功能:一是產生標準1Hz的脈沖信號;二是提供校正電路的校正信號。因為74LS90是二-五-十進制計數器,所以采用三片計數器級聯就可以實現上述功能,即三片級聯可以獲得所需的頻率信號。電路圖如圖3所示。

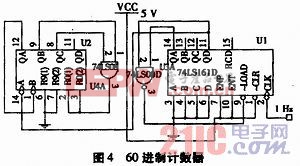

數字電子鐘需要兩個60進釗計數器分別作為“分”、“秒”計數器,還需要一個24進制計數器作“小時”計數器。60進制計數器采用一片74LS90和一片74LS161級聯實現。74LS161用作“秒計數器”個位,所以將其設計成十進制計數器,這里用反饋預置法實現。即當計數器計到1001時,將74LS161的QA端和QD端,分別接至一個與非門的輸入端,將與非門的輸出端送至預置端LD,這樣就可實現十進制計數。“秒計數器”的十位用74LS90實現,所以將其設計成六進制的計數器,用反饋清零法實現。即當計數器計到0110時,將74LS90的QB端和QC端,分別接至一個與門的輸入端,將與門的輸出端送至清零端R01和R02,由此實現六進制計數功能。其電路圖如圖4所示。

評論